E1/T1, E3/T3, ECL interface

Features

- Sixteen E1 / T1 line interfaces

- Four E3 / T3 line interfaces

- Sixteen ECL differential inputs / outputs

- Large Xilinx FPGA (provided by EDT PCIe8 LX, PCI GS, or PCI SS main board – see details below)

- Two large synchronous static memory banks or one memory bank up to 1 GB (also provided by main board – see details below)

- LVDS external clock that can be used to synchronize the output data

- Sixteen independent DMA channels to host memory

- Fast transfers using a 66 MHz 32-bit PCI

Applications

- Telecommunications network monitoring

- Telecommunications switching

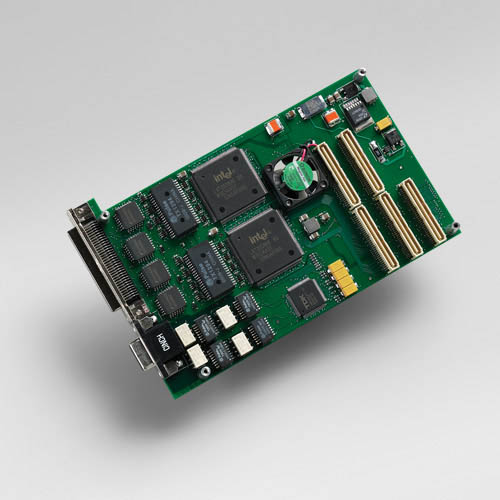

Description

The Combo Mezzanine board pairs with a PCI / PCIe main board (EDT PCIe8 LX, PCI GS, or PCI SS). The board pair supports the processing of large amounts of telecom serial or ECL data for complex, user-defined applications. The high-speed 16-channel DMA controller allows flexible access to host memory. The main board supplies the DMA, memory, and programmable FPGA resources (see ordering options below); EDT provides FPGA configuration files.

Specifications

| PCI / PCIe bus compliance | Related to main board; see datasheet / specifications for the main board you are using. |

| UI FPGA (main board) | PCI SS: Xilinx XCV1000E or optional XCV600E, XCV2000E PCI GS: Xilinx XC2VP50 or optional XC2VP70 User definable LED Debug connector, 20-pin .100″ x .100″ square pins, two rows |

| Memory (main board) | |

| Local | PCI SS: Two 256K x 36-bit word synchronous static RAM or optional no RAM, 512K x 36-bit word RAM, or 1M x 36-bit word RAM PCI GS: 1M x 36-bit word synchronous static RAM or optional 2M x 36-bit word RAM (with XC2VP70) |

| Dynamic | PCI GS: 200-pin SODIMM socket for optional DDR memory module. Up to 1 gigabyte. |

| ECL |

|

| E3 / T3 |

|

| E1 / T1 |

|

| External connectors | High-density 68-pin AMP™ connector (part number 787169-7) High-density 15-pin AMP™ receptacle (part number 748390-5) |

| Physical | Dimensions: 4.2″ x 6.6″ |

|

Environmental

|

|

| Temperature

Humidity |

Operating: 0° to 44° C Non-operating: -40° to 70° C Heat output: TBD Operating: 1% to 90% non-condensing at 40° C Non-operating: 95% non-condensing at 45° C |

| Power | 2 amps at 5V |

Software

Device drivers for Windowstm and Linux are included with the purchase of the Combo Mezzanine. Contact us about other operating systems.

Support

EDT provides several levels of customer support, from phone consultation to custom design of hardware, firmware, or software, at hourly rates. Technical support is also provided though the Support section of this web site.

Third-party support

Technisys, Inc. provides a family of interface panels designed to provide an easy and economical method of interfacing to the EDT Combo Mezzanine and other EDT products. See their web site, www.tsys-inc.com

Ordering

Ordering options are only on the main board and are listed below. To order, contact our sales department or your distributor. Be sure to specify which cable (if any) will be needed.

Main board options

PCI SS main board with…

FPGA (Xilinx Virtex™-E): XCV600E / XCV2000E

Static memory (RAM): None / 512K x 36-bit word / 1M x 36-bit word

…or…

PCI GS main board with…

FPGA (Xilinx Virtex™-II Pro): XC2VP50 / XC2VP70

Static memory (RAM): 1M x 36-bit word (XC2VP50) / 2M x 36-bit word (XC2V70)

Dynamic memory (RAM): None / 1 gigabyte DDR

…or…

PCIe8 LX / FX / SX main board – for options, contact EDT.