# PCI CD/CDa

# **Configurable DMA Interface**

for PCI Local Bus Computers

May 2007 008-00965-08

The information in this document is subject to change without notice and does not represent a commitment on the part of Engineering Design Team, Inc. The software described in this document is furnished under a license agreement or nondisclosure agreement. The software may be used or copied only in accordance with the terms of the agreement.

Engineering Design Team, Inc. ("EDT"), makes no warranties, express or implied, including without limitation the implied warranties of merchantibility and fitness for a particular purpose, regarding the software described in this document ("the software"). EDT does not warrant, guarantee, or make any representations regarding the use or the results of the use of the software in terms of its correctness, accuracy, reliability, currentness, or otherwise. The entire risk as to the results and performance of the software is assumed by you. The exclusion of implied warranties is not permitted by some jurisdictions. The above exclusion may not apply to you.

In no event will EDT, its directors, officers, employees, or agents be liable to you for any consequential, incidental, or indirect damages (including damages for loss of business profits, business interruption, loss of business information, and the like) arising out of the use or inability to use the software even if EDT has been advised of the possibility of such damages. Because some jurisdictions do not allow the exclusion or limitation of liability for consequential or incidental damages, the above limitations may not apply to you. EDT's liability to you for actual damages for any cause whatsoever, and regardless of the form of the action (whether in contract, tort [including negligence], product liability or otherwise), will be limited to \$50 (fifty U.S. dollars).

No part of this manual may be reproduced or transmitted in any form or by any means, electronic or mechanical, without the express written agreement of Engineering Design Team, Inc.

Copyright © Engineering Design Team, Inc. 1997–2007. All rights reserved.

EDT and Engineering Design Team are trademarks of Engineering Design Team, Inc.

Xilinx is a registered trademark of Xilinx, Inc.

# Contents

| The PCI Bus Configurable DMA Interface<br>Related Manuals                                                                                                          |                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                                                                                                                                                                    |                                                                                                    |

| About the DMA Interface                                                                                                                                            | 3                                                                                                  |

| About the Software and Firmware                                                                                                                                    | 4                                                                                                  |

| CDa FPGA Configuration Files                                                                                                                                       |                                                                                                    |

| CD-20 and CD-60 FPGA Configuration Files                                                                                                                           |                                                                                                    |

| Software Initialization Files                                                                                                                                      |                                                                                                    |

| The PCD Device Driver                                                                                                                                              |                                                                                                    |

| FPGA Configuration Files                                                                                                                                           |                                                                                                    |

| Software Initialization Files                                                                                                                                      |                                                                                                    |

| Sample Applications and Utilities                                                                                                                                  |                                                                                                    |

| Sample Applications                                                                                                                                                |                                                                                                    |

| Utility Files                                                                                                                                                      |                                                                                                    |

| Testing Files                                                                                                                                                      |                                                                                                    |

| Building Applications                                                                                                                                              |                                                                                                    |

|                                                                                                                                                                    |                                                                                                    |

| Configuring the PCI CD/CDa                                                                                                                                         | 8                                                                                                  |

| Checking the PCI FPGA Firmware                                                                                                                                     | 8                                                                                                  |

| Loading the UI FPGA Firmware and Configuring the PCI CD/CDa                                                                                                        | 9                                                                                                  |

| Using Custom FPGA Configuration Files                                                                                                                              | 9                                                                                                  |

|                                                                                                                                                                    |                                                                                                    |

| Lesting                                                                                                                                                            | 10                                                                                                 |

| Testing                                                                                                                                                            |                                                                                                    |

| Generating an Output Clock                                                                                                                                         |                                                                                                    |

|                                                                                                                                                                    | 11                                                                                                 |

| Generating an Output Clock                                                                                                                                         | 11<br>11                                                                                           |

| Generating an Output Clock<br>PCI CDa<br>PCI CD                                                                                                                    | 11<br>11<br>11                                                                                     |

| Generating an Output Clock<br>PCI CDa<br>PCI CD<br>Hardware Interface Protocol                                                                                     | 11<br>11<br>11<br>13                                                                               |

| Generating an Output Clock<br>PCI CDa<br>PCI CD<br>Hardware Interface Protocol<br>Electrical Interface                                                             | 11<br>11<br>11<br>13<br>13                                                                         |

| Generating an Output Clock<br>PCI CDa<br>PCI CD<br>Hardware Interface Protocol<br>Electrical Interface<br>RS-422                                                   | 11<br>11<br>11<br>13<br>13<br>14                                                                   |

| Generating an Output Clock<br>PCI CDa<br>PCI CD<br>Hardware Interface Protocol<br>Electrical Interface<br>RS-422<br>LVDS                                           | 11<br>11<br>13<br>13<br>13<br>14<br>14                                                             |

| Generating an Output Clock<br>PCI CDa<br>PCI CD<br>Hardware Interface Protocol<br>Electrical Interface<br>RS-422<br>LVDS<br>Signals                                | 11<br>11<br>13<br>13<br>13<br>14<br>14<br>15                                                       |

| Generating an Output Clock<br>PCI CDa<br>PCI CD<br>Hardware Interface Protocol<br>Electrical Interface<br>RS-422<br>LVDS<br>Signals                                | 11<br>11<br>13<br>13<br>14<br>14<br>15<br>16                                                       |

| Generating an Output Clock<br>PCI CDa<br>PCI CD<br>Hardware Interface Protocol<br>Electrical Interface<br>RS-422<br>LVDS<br>Signals                                | 11<br>11<br>13<br>13<br>14<br>14<br>15<br>16                                                       |

| Generating an Output Clock<br>PCI CDa<br>PCI CD<br>Hardware Interface Protocol<br>Electrical Interface<br>RS-422<br>LVDS<br>Signals                                | 11<br>11<br>13<br>13<br>14<br>14<br>14<br>15<br>16<br>18                                           |

| Generating an Output Clock<br>PCI CDa<br>PCI CD<br>Hardware Interface Protocol<br>Electrical Interface<br>RS-422<br>LVDS<br>Signals<br>Timing<br>Connector Pinouts | 11<br>11<br>13<br>13<br>13<br>14<br>14<br>15<br>16<br>18<br>19                                     |

| Generating an Output Clock<br>PCI CDa<br>PCI CD<br>Hardware Interface Protocol<br>Electrical Interface<br>RS-422<br>LVDS<br>Signals<br>Timing<br>Connector Pinouts | 11<br>11<br>13<br>13<br>14<br>14<br>15<br>16<br>18<br>19<br>19                                     |

| Generating an Output Clock                                                                                                                                         | 11<br>11<br>13<br>13<br>14<br>14<br>15<br>16<br>18<br>19<br>21                                     |

| Generating an Output Clock                                                                                                                                         | 11<br>11<br>13<br>13<br>14<br>14<br>15<br>16<br>18<br>19<br>21<br>21                               |

| Generating an Output Clock                                                                                                                                         | 11<br>11<br>13<br>13<br>14<br>14<br>14<br>15<br>16<br>19<br>21<br>21<br>22<br>23                   |

| Generating an Output Clock                                                                                                                                         | 11<br>11<br>13<br>13<br>14<br>14<br>14<br>14<br>14<br>16<br>11<br>21<br>21<br>21<br>22<br>23<br>23 |

|     | Scatter-gather DMA Current Address Register           | 24 |

|-----|-------------------------------------------------------|----|

|     | Scatter-gather DMA Next Address Register              | 24 |

|     | Scatter-gather DMA Current Count and Control Register |    |

|     | Scatter-gather DMA Next Count and Control Register    | 25 |

|     | PLL Programming Register                              |    |

|     | Flash ROM Address Register                            |    |

|     | Flash ROM Data Register                               |    |

|     | PCI Interrupt and UI Xilinx Configuration Register    |    |

|     | PCI Interrupt Status Register                         |    |

|     | UI Xilinx Data Register                               |    |

|     | UI Xilinx Registers                                   |    |

|     | Command Register                                      |    |

|     | Data Path Status Register                             |    |

|     | Funct Register                                        |    |

|     | Stat Register                                         |    |

|     | Stat Polarity Register                                |    |

|     | Direction Control Registers                           |    |

|     | Programmed I/O Low Register                           |    |

|     | Programmed I/O High Register                          |    |

|     | Interface Configuration Register                      |    |

|     | PCI CDa Registers                                     |    |

|     | PLL Programming Register                              |    |

|     | PLL Divider Register                                  |    |

|     | Output Data Valid Delay Register                      |    |

|     | LED Control Register                                  |    |

|     |                                                       |    |

| Ref | ferences                                              | 37 |

|     |                                                       |    |

# The PCI Bus Configurable DMA Interface

The Configurable DMA Interface (PCI CD/CDa) is a single-slot DMA input/output interface for PCI Bus-based computer systems. It is designed for continuous input or output between a user device and PCI Bus host memory. This interface is typically used to move data to or from a PCI Bus host computer to devices such as scanners, plotters, imaging devices, or research prototypes.

The basic configuration of the PCI CD/CDa uses a bidirectional single-channel 16-bit parallel protocol. In a 66 MHz PCI Bus slot, it can transfer up to 210 MB per second. It is available using either RS-422 or LVDS signal levels. A variety of other options are also available: a 16-channel synchronous serial protocol, a 4-channel synchronous serial protocol, a single channel synchronous serial protocol, or an 8-bit parallel protocol. Manuals describing these options are listed in Related Manuals on page 2.

The PCI CD-20 (RS-422) and the PCI CD-60 (LVDS) are older versions of the PCI CDa that use different versions of the DMA engine, but have many of the same capabilities. However, they operate only in a 33 MHz PCI Bus slot.

The PCI CD/CDa implements the DMA interface using two Xilinx field-programmable gate arrays, referred to as the PCI Xilinx and the UI (user interface) Xilinx.

- The *PCI Xilinx* communicates with the host computer over the PCI Bus. It transfers data between the board and the host computer, and loads its firmware on powerup from flash ROM.

- The UI Xilinx transfers data between the user device and the board, through the connector. The UI Xilinx may also process the data in some manner, depending on the application.

Each Xilinx must be loaded with the firmware specific to the chosen interface, and the firmware in one Xilinx must be compatible with the firmware in the other. The PCI CD/CDa comes configured for the interface you ordered; a list of the firmware files provided is available in About the Software and Firmware on page 3, and instructions for loading them, if necessary, are provided in Configuring the Board on page 7.

When data comes in from the user device, the UI Xilinx sends it to input and output FIFO buffers, which smooth data transfer between the PCI bus and the user device, as well as accommodating data during the transition from one DMA to the next. DMA transfers are queued in hardware, minimizing the amount of FIFO required. The PCI CD/CDa uses 4 KB input and output FIFOs; the PCI CDa implements these FIFOs internally in the UI Xilinx; the PCI CD-20 and CD-60 implement them externally.

Either the PCI CD/CDa interface or your own device can generate the receive or transmit timing, or each can generate its own transmit timing.

#### **Related Manuals**

The following related publications may prove useful:

#### Manual

URL

Detailed documentation on EDT's C software library routines, helpful for writing your applications, is available in either HTML or PDF formats:

EDT DMA Software Library (HTML) www.edt.com/api

EDT DMA Software Library (PDF) www.edt.com/manuals/misc/api.pdf

In addition, the following manuals provide information on other options available for the PCI CD/CDa boards:

SSD16 16-channel Synchronous Serial I/O www.edt.com/manuals/PCD/ssd16.pdf

Sixteen channel bidirectional synchronous serial interface for the PCI CD/CDa.

PCD8 8-bit Parallel I/O www.edt.com/manuals/PCD/pcd8.pdf

Eight-bit bidirectional parallel interface for the PCI CD/CDa.

SSD4 4-channel Synchronous Serial I/O www.edt.com/manuals/PCD/ssd4.pdf

Single-, dual-, or four-channel synchronous serial input with multiplexed single-channel DMA for the PCI CD-20 and CD-60 only.

#### SSDIO Synchronous Serial I/O www.edt.com/manuals/PCD/ssdio.pdf

Dual-channel synchronous serial input/output on either the rising or the falling clock edge, for the PCI CD-20 and CD-60 only.

# About the Software and Firmware

The PCI CD/CDa comes with firmware files to configure the two Xilinxes (having the extension .bit), a variety of utility applications, a firmware file to use for testing the board, and software initialization files (having the extension .cfg) to use to initialize the board for each configuration.

The PCI Xilinx firmware files are in the flash subdirectory of the EDT top-level distribution directory. UI Xilinx firmware files are in the bitfiles subdirectory of the EDT top-level distribution directory.

The following files are included:

#### CDa FPGA Configuration Files

| cdal.bit | PCI Xilinx configuration file for single-channel, 16-bit parallel input/output for RS-422 or |

|----------|----------------------------------------------------------------------------------------------|

|          | LVDS.                                                                                        |

Either of the two UI Xilinx configuration files can be used with the PCI Xilinx configuration file provided:

| pcda.bit | UI Xilinx configuration file for single-channel, 16-bit parallel input/output for RS-422 or LVDS. |

|----------|---------------------------------------------------------------------------------------------------|

|          |                                                                                                   |

#### xtest.bit UI Xilinx configuration file for running the test described in Testing on page 10

#### CD-20 and CD-60 FPGA Configuration Files

The PCI Xilinx must be loaded with the FPGA configuration file intended for its model:

|                     | -                                                                                                       |

|---------------------|---------------------------------------------------------------------------------------------------------|

| pcd20.bit           | PCI Xilinx configuration file for 16-bit parallel input/output for the PCI CD-20 (RS-422).              |

| pcd60.bit           | PCI Xilinx configuration file for 16-bit parallel input/output for the PCI CD-60 (LVDS).                |

| Any of the UI Xilin | x configuration files can be combined with either of the PCI Xilinx configuration files:                |

| pcd_src.bit         | UI Xilinx configuration file for 16-bit parallel input/output, synchronized to the PCI CD source clock. |

| pcd_looped.bit      | UI Xilinx configuration file for 16-bit parallel input/output, synchronized to an external clock.       |

xtest.bit UI Xilinx configuration file for running the test described in Testing on page 10.

#### Software Initialization Files

Sample software initialization files for all board configurations are in the pcd\_config subdirectory of the distribution directory.

Software initialization files are editable text files that you can customize for your own applications.

| pcda.cfg       | Software initialization file for single-channel, 16-bit parallel input/output for RS-422 or LVDS, for the PCI CDa only.                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| pcd_src.cfg    | Software initialization file for 16-bit parallel input/output, synchronized to the PCI CD source clock, for the PCI CD-20 and CD-60 only. |

| pcd_looped.cfg | Software initialization file for 16-bit parallel input/output, synchronized to an external clock, for the PCI CD-20 and CD-60 only.       |

#### **FPGA Configuration Files**

The main board implements the DMA interface using two field-programmable gate arrays (FPGAs), referred to as the PCI FPGA and the UI (user interface) FPGA:

- The *PCI FPGA* communicates with the host computer over the PCI Bus. It implements the DMA engine, which transfers data between the board and the host computer, and loads its firmware on powerup from flash ROM located on the main board.

- The *UI FPGA* transfers data between the user device and the PCI FPGA; in some instances, it also sends the data to the mezzanine board. The UI FPGA or mezzanine board may also process the data in some manner, depending on the application.

- In addition, some mezzanine boards also have an FPGA which must be loaded with the correct firmware.

FPGA configuration files define the firmware required for the PCI FPGA and the UI FPGA. The PCI FPGA firmware files are in the flash subdirectory of the EDT top-level distribution directory. UI FPGA firmware files are in the bitfiles subdirectory of the EDT top-level distribution directory. mezzanine board configuration files, if any, are in the mezzanine board-specific subdirectory.

Each FPGA must be loaded with the firmware specific to the chosen interface, and the firmware in one FPGA must be compatible with the firmware in the other. By default, the correct FPGA configuration file for the PCI FPGA is loaded at the factory. However, you'll need to load the required FPGA configuration file for the UI FPGA yourself.

The firmware files specific to your PCI CD/CDa are listed at the beginning of this section. Instructions for loading them are provided in Configuring the PCI CD/CDa.

#### The PCD Device Driver

The PCD device driver is the software running on the host that allows the host operating system to communicate with the PCI CD/CDa. The driver is loaded into the kernel upon installation, and thereafter runs as a kernel module. The driver name and subdirectory is specific to each supported operating system; the installation script handles those details for you, automatically installing the correct device driver in the correct operating system-specific manner.

#### **Software Initialization Files**

Software initialization files (having the extension .cfg) are editable text files that run like scripts to configure EDT boards so that they are ready to perform DMA. The commands in a software initialization file are defined in a C application named initpcd. When you invoke initpcd, you specify which software initialization file to use with the -f flag.

A typical software initialization file loads an FPGA configuration file into the UI FPGA and sets up various registers to prepare the board for DMA transfers. Some software initialization files may also load an FPGA configuration file into an FPGA residing on the mezzanine board.

A variety of software initialization files are included with the EDT software, at least one of which is customized for each main board or main board / mezzanine board combination — that is, each FPGA configuration file has a matching software initialization file. Software initialization files are located in the pcd\_config subdirectory of the EDT top-level distribution directory. The software initialization files specific to your PCI CD/CDa are listed at the beginning of this section. Instructions for their use are provided in Configuring the PCI CD/CDa.

Commands defined in initpcd and typically found in software initialization files allow for specific FPGA configuration files to be loaded (for example, bitfile:), write specified hexadecimal values to specified registers (for example, command\_reg:), enable or disable byte-swapping or short-swapping to accommodate different operating systems' requirements for bit ordering (for example, byteswap:), or invoke arbitrary commands (for example, run\_command:). If the mezzanine board you're using has

an FPGA, you can load the appropriate firmware on it by running the command mezzload, which determines the appropriate firmware for the specific mezzanine board in your system.

#### For example:

```

bitfile: ssd16io.bit

command_reg: 0x08

byteswap: 1

run_command: set_ss_vco -F 1000000 2

run_command: mezzload

```

For complete usage details, enter initpod --help.

C source for initped is included so that you can add your own commands, if you wish. You can then edit your own software initialization file to use your new commands and specify that initped use your new file when configuring your board. If you would like us to include your new software initialization commands in subsequent releases of initped, send mail to tech@edt.com.

#### **Sample Applications and Utilities**

Along with the driver, the FPGA configuration files, and the software initialization files, the software CD includes a number of applications and utilities that you can use to initialize and configure the board, access registers, or test the board. For many of these applications and utilities, C source is also provided, so that you can use them as starting points to write your own applications. The most commonly useful are described below; see the README file for the complete list.

**NOTE** Software is updated regularly; the latest versions are available on our website at www.edt.com/software.html. We encourage you to use the latest versions for new installations. For existing applications, upgrade only if you have a specific reason to do so.

#### Sample Applications

| rd16           | Performs simple multichannel ring buffer input.                                                                                                                                 |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wrl6           | Performs simple multichannel ring buffer output.                                                                                                                                |

| simple_read    | Performs DMA input without using ring buffers. Data is therefore subject to interruptions, depending on system performance.                                                     |

| simple_write   | Performs DMA output without using ring buffers. Data is therefore subject to interruptions, depending on system performance.                                                    |

| simple_getdata | Serves as an example of a variety of DMA-related operations, including reading the data from the connector interface and writing it to a file, as well as measuring input rate. |

| simple_putdata | Serves as an example of a variety of DMA-related operations, including reading data from a file and writing it out to the connector interface.                                  |

| test_timeout   | Under normal operation, timeouts cancel DMA transfers. This application exemplifies giving notification when a timeout occurs, without canceling DMA                            |

| set_ss_vco     | A utility for programming the output clock or clocks on the PCI CD/CDa to specific frequencies used by the UI FPGA for input and output.                                        |

| Utility Files  |                                                                                                                                                                                 |

| initpcd        | A utility for initializing and configuring the PCI CD/CDa.                                                                                                                      |

pdb Utility application that enables interactive reading and writing of the PCI SS/GS UI FPGA registers.

#### **Testing Files**

A variety of files — C source, executables, and FPGA configuration files — are available to test the boards. Their uses are described in the documents listed under the heading Testing Procedures. They include at least:

sslooptest Tests most PCI SS- and PCI GS-based boards. Determines the board model and selects the loopback test to run, then runs it.

xtest Tests the PCI CD and CDa boards, and the single-channel DMA interface for the PCI SS and PCI GS main boards.

#### **Building Applications**

Executable and PCD source files are at the top level of the EDT PCD driver distribution directory. If you need to rebuild an application, therefore, run make in this directory.

Windows and Solaris users must install a C compiler. For Windows, we recommend the Microsoft Visual C compiler; for Solaris, the Sun WorkShop C compiler. Linux users can use the gcc compiler typically included with your Linux installation. If Solaris or Windows users wish to use gcc, contact tech@edt.com.

After you've built an application, use the --help command line option for a list of usage options and descriptions.

# **Configuring the Board**

For your EDT board to operate as you require, it must be loaded with the appropriate FPGA configuration files for both FPGAs. The PCI FPGA is loaded from flash ROM, which is shipped from the factory already loaded with the appropriate FPGA configuration file; however, you must load the UI FPGA yourself.

Before loading the UI FPGA, however, you may wish to check the firmware in the PCI FPGA to ensure that it is correct and up-to-date.

#### Checking the PCI FPGA Firmware

When upgrading to a new device driver, or switching to a FPGA configuration file with special functionality, you may also need to reprogram the PCI interface flash PROM using pciload.

The following procedure applies to standard firmware only. If you are running a custom firmware file and need to update it, first get a custom firmware configuation file from EDT.

**NOTE** The presence of a newer version of the firmware with a new driver doesn't necessarily mean that the firmware must be updated; if a package contains a mandatory upgrade, it is prominently stated in the README file.

On UNIX systems, pciload is an application in the installation directory /opt/EDTpcd.

On Windows systems, double-click the Pcd Utilities icon to bring up a command shell in the installation directory \EDT\Pcd.

On Macintosh systems, pciload is an application in the installation directory /Applications/EDT/pcd.

To see currently installed and recognized EDT boards and drivers, enter:

pciload

The program outputs the date and revision number of the firmware in the PROM.

To compare the PCI FPGA firmware in the package with the one already loaded on the board, enter:

pciload verify

The program compares the firmware in the PROM against the firmware file in the installation directory. If they match, there's no need to upgrade the firmware. If they differ, you'll see error messages. This does not necessarily indicate a problem; if your application is operating correctly, you may not need to upgrade the firmware.

If you wish to update the standard firmware, enter:

pciload update

1. To upgrade or switch to a custom firmware file, enter:

pciload firmware\_filename

replacing *firmware\_filename* with the name of the PCI FPGA configuration file, with or without the .bit file extension.

**NOTE** If the host computer holds more than one board, you can specify the correct board to load with the optional *unit\_number* argument (by default, 0 for the first or only board in a host):

pciload -u unit\_number filename

2. At the prompt, press **Enter** to confirm the loading operation. (If the file date is older than the PROM ID date, you may need to press **Enter** twice.)

The board reloads the firmware from the PROM only during power-up, so after running pciload, the old firmware remains in the PCI FPGA until the system has power-cycled.

NOTE Updating the firmware requires cycling power, not simply rebooting.

For a list of all pciload options, enter:

pciload --help

#### Loading the UI FPGA Firmware and Configuring the PCI CD/CDa

The utility initped loads the UI FPGA configuration files, programs the registers, sets the clocks (if necessary), and gets the PCI CD/CDa mezzanine board ready to perform DMA. This utility takes, as an argument, a software initialization file, and then automatically runs the pertinent commands.

If you use initped to configure the PCI CD/CDa, your application can concern itself solely with performing DMA and other application-specific operations; it will therefore omit PCI CD/CDa-specific operations and be portable to other EDT boards that peform DMA.

To configure the PCI CD/CDa, enter:

initpcd -u unit\_number -f pcd\_config/filename.cfg

replacing unit\_number with the number of the board (by default, 0), and replacing *filename* with one of the initialization files listed in About the Software and Firmware; for example:

initpcd -f pcda.cfg

**NOTE** Software initialization files are editable text files. If the files provided don't meet your needs, copy and modify the one that's closest to your required configuration, then run initped with your new file.

#### **Using Custom FPGA Configuration Files**

You can substitute your own FPGA configuration file, if necessary. If you wish to develop your own VHDL design, contact EDT. When you're done, be sure to create a new software initialization file for your new firmware file and update the pcd\_config directory to include it.

# Testing

When you run this test, the PCI CD/CDa is configured with the FPGA configuration file xtest.bit. For normal operation, reconfigure the board with initped after completing the test, as described in Loading the UI FPGA Firmware and Configuring the PCI CD/CDa on page 8, to reconfigure the board with the correct UI Xilinx configuration file.

To verify that installation was successful and that the PCI CD/CDa is operating correctly, run xtest. At a command prompt, enter:

xtest -i 4096

The number following -i specifies the number of bytes to test. The PCI CD returns test status information. The following is an example of proper behavior, although details will vary:

```

reading 4096 words

buf at 820000

testing dirreg at 4 4

testing dirout at 8 8

testing dirin at 8 c

testing ctlout at a a

testing ctlin at a e

Calling DMA read 8192 at 820000

return to do read:

read returned length 8192

Done.

checking data

4096 words 0 errors

buf 0 820000

buf 1 920000

reading 100 buffers of 1048576 bytes from unit 0 with 2 bufs

return to start: starting read at 820000

starting read at 920000

hit return to continue:

counter0 4628 2362958141 counter1 4628 3122437420 freq 0 266230000

dtime 759479279.000000 ticktime 266230000.000000

time is 2.852719 sec

36757077.671371 bytes/sec

```

Problems are indicated by the string ERROR – followed by an error message. If you do not see such a string in the output, then the test completed satisfactorily.

### **Generating an Output Clock**

The PCI CD/CDa has a programmable frequency generator, allowing you to specify precisely the frequency at which to transmit data.

#### PCI CDa

The PCI CDa has one programmable clock with a range of 168 Hz - 100 MHz. Most frequencies between these extremes can be achieved with little error. (Some FPGA configuration files allow an extended range of up to 200 MHz.)

The programmable clock is implemented with an ICS307-02 clock generator followed by a 14-bit programmable divider. The reference clock to the ICS307-02 is 10.3861 MHz. For details on the ICS307-02, consult Integrated Circuit Systems.

**NOTE** The library routine set\_ss\_vco.c includes an example of setting the output clock frequency.

The following three library routines, documented in the EDT DMA Software Library, help compute the output clock frequency:

edt\_find\_vco\_frequency\_ics307

Computes the PLL parameter for the ICS307 chip, based on an input clock frequency and a target frequency.

edt\_set\_out\_clk\_ics307

Sets the frequency output using parameters computed by edt\_find\_vco\_frequency\_ics307.

edt\_set\_frequency\_ics307

A convenience function to to set the frequency on the desired channel by first calling edt\_find\_vco\_frequency\_ics307 or edt\_find\_vco\_frequency\_ics307\_nodivide, then edt\_set\_out\_clk\_ics307.

#### PCI CD

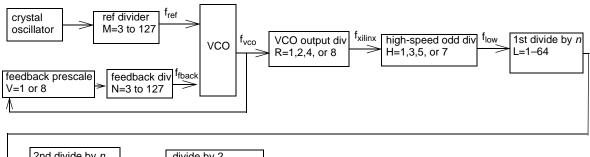

The output clock is generated from a phase-locked loop (PLL) oscillator, a reference crystal, and programmable dividers. Because each of these components has physical limits, it may not be possible to get exactly the frequency desired. To get the expected results, you need to understand how the clock generator operates. Figure 1 diagrams how the final value is generated, using the following notation:

| f <sub>xtal</sub>   | 10 MHz (PCI CD-20 or 30 MHz (PCI CD-60)                                                                                                                                            |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f <sub>ref</sub>    | The PLL reference frequency must be between 200 KHz and 5.0 MHz.                                                                                                                   |

| f <sub>vco</sub>    | The VCO output frequency must be between 50 MHz and 250 MHz.                                                                                                                       |

| f <sub>fback</sub>  | The VCO varies $f_{vco}$ until the feedback frequency matches the PLL reference frequency.                                                                                         |

| f <sub>xilinx</sub> | The input frequency into the high speed odd divider must be less than 100 MHz.                                                                                                     |

| f <sub>low</sub>    | The divide by <i>n</i> counter input frequency must be less than 30 MHz. If L and X are both set to 1, then frequencies to 100 MHz can be passed to the final divide-by-two block. |

| f <sub>out</sub>    | This final divide by two assures a 50% output clock duty cycle.                                                                                                                    |

The formula for calculating the output frequency is:

$$f_{out} = (N * V * f_{xtal}) / (m * R * H * L * X * 2)$$

Figure 1. Setting the Output Clock Frequency

For example, for an output clock of 15 MHz using a PCI CD-20 ( $f_{xtal} = 10$  MHz), the following numbers work, although they are not unique: N=60, V=1, M=10, R=2, H=1, L=1, X=1

For an output clock of 125 Hz in a PCI CD-20 (f<sub>xtal</sub> = 10 MHz): N=50, V=1, M=10, R=8, H=5, L=50, X=100

The output clock has a wide range of values, but the frequency limitations at different stages limits the ultimate ability to exactly reach any specific frequency.

For example, the PLL reference frequency can be as low as 200 KHz, which would seem to allow steps of 200,000 in the VCO output. Unfortunately, since the maximum VCO output is 50 MHz and the *n*-programmable divider only goes to 127, the loop cannot lock unless V is set to 8, giving 1.6 MHz minimum steps. If, however, R is set to 8, we can get 200 KHz steps at  $f_{xilinx}$ . The lowest frequency in this case is at N=32 (6.4 MHz) to N=127 (25.4 MHz), in 200 KHz steps.

The following three library routines, documented in the EDT DMA Software Library, help compute the output clock frequency:

```

edt_find_vco_frequency

```

Computes the phase-locked loop parameters necessary to match or approximate the supplied target frequency.

edt\_set\_pll\_clock

Sets the phase-locked loop circuit to the value computed by edt\_find\_vco\_frequency. Includes debugging information.

edt\_set\_out\_clock

Sets the phase-locked loop circuit to the value computed by edt\_find\_vco\_frequency. Does not include debugging information.

### **Hardware Interface Protocol**

This section describes how to connect your device to a PCI CD/CDa interface, including the electrical characteristics of the signal, the signal descriptions, the timing specifications, and the connector pinout.

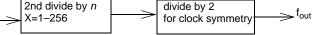

#### **Electrical Interface**

The PCI CD/CDa uses differential data transmission to transmit data at very high rates over long distances through noisy environments. Differential transmission nullifies the effects of ground shifts and noise. These effects appear as common mode voltages on the transmission line and are rejected by the receiver. A typical balanced differential circuit is shown below.

#### Figure 2. Balanced Differential Circuit

The interface is implemented with 32 signals (PCI CD) or 35 signals (PCI CDa), each implemented as a differential pair of wires.

#### RS-422

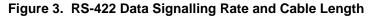

The PCI CD-20 and PCI CDa RS-422 DMA interface protocols use RS-422 signal levels. RS-422 is defined by the Electronic Industries Association to provide robust high-speed data transmission. It allows signaling rates up to 10 MHz for short cables of up to 40 feet (12 meters) and cables of up to 4000 feet (1219 meters) at 100 KHz, as shown in Figure 3:

Data Rate (bits per second)

For further information, see the EIA RS-422-A standard, Electrical Characteristics of Balanced Voltage Digital Interface Circuits.

#### LVDS

The PCI CD-60 and PCI CDa LVDS DMA interface protocols use low-voltage differential signaling, a standard for faster signaling at lower power, compatible with IEEE 1596.3 SCI LVDS standard, and conforming to ANSI/TIA/EIA-644 LVDS standard.

For details, also see the LVDS Owner's Manual.

#### Signals

The hardware flow control protocol assumes that FIFO or memory buffers on both ends implement almost-full and almost-empty thresholds. Therefore, when a BNR (board not ready) or DNR (device not ready) signal is sent to the transmitting device, the receiver can still accommodate enough data to allow for cable delay and synchronization.

| Table 1. Signa | ls |

|----------------|----|

|----------------|----|

| Signal            | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DAT(15:0)         | I/O | Sixteen bidirectional data lines for DMA data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| STAT(3:0)         | I   | Four general-purpose control inputs. Any can be enabled to interrupt the PCI bus host.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| FUNCT(3:0)        | 0   | Four general-purpose program control outputs. Can be used to reset the user device or indicate DMA direction for bidirectional devices.                                                                                                                                                                                                                                                                                                                                                                                           |  |

| SENDT             | 0   | Send Timing is a constant clock driven by the DMA interface that the user device can use (though it need not) to generate the receive timing. See Table 2 for timing specifications. The source for SENDT can be either:                                                                                                                                                                                                                                                                                                          |  |

|                   |     | <ul> <li>the internal oscillator (the default when using pcd_src.bit);</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                   |     | <ul> <li>the signal RXT when the PCI CD is using pcd_looped.bit, or the PCI CDa has<br/>set bit 1 (SELRXT) in the Interface Configuration Register; or</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 |  |

|                   |     | • the PLL when the PCI CD is using pcd_src.bit, or the PCI CDa has set bit 7, PLLCLK, in the Funct Register.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| RXT               | I   | Receive Timing is an input to the DMA interface. This is the clock used to synchroniz<br>input data and control signals. This signal can be equal to or less than the SENDT<br>frequency of the board in use. It is best, although not required, that this signal is a<br>continuous clock. Data clocked into the DMA interface must propagate through<br>pipelining registers before it can be transferred into PCI bus memory. If the RXT cloc<br>stops, data is left in this pipe instead of being transferred to host memory. |  |

| ТХТ               | 0   | Transmit Timing is an output from the DMA interface. TXT synchronizes the DMA output data and control signals. TXT is an inverted copy of SENDT, which provides maximum setup and hold on rising edge.                                                                                                                                                                                                                                                                                                                            |  |

| IDV               | I   | Input Data Valid is asserted by the device synchronous with RXT, to tell the DMA interface that data on the DAT(15:0) signals are valid and must be registered and transferred to the PCI bus memory. The DMA interface will accomplish this unless the BNR signal has been asserted for >32 IDV signals.                                                                                                                                                                                                                         |  |

| BNR               | 0   | Bus Not Ready is asserted by the DMA interface synchronous with TXT when 32 bytes or fewer of data space remains for input data from the device. This warns you to stop the data transfer or prepare for overflow.                                                                                                                                                                                                                                                                                                                |  |

| OUTPUT<br>DISABLE | I   | Disables the data outputs when more than one PCI CD board is connected to the same cable. In order to use this signal, you must set the Enable Output Control bit in the Stat Polarity Register. TTL-compatible. PCI CD only.                                                                                                                                                                                                                                                                                                     |  |

| ODV               | 0   | Output Data Valid is asserted by the DMA interface when it has placed valid output data on DAT(15:0). ODV is asserted synchronously with the TXT clock, and only if the DNR signal is not asserted.                                                                                                                                                                                                                                                                                                                               |  |

| DNR               | I   | Device Not Ready is asserted by the device synchronous with the RXT clock when the user device is about to run out of space for storing data from the DMA interface. The amount of overrun buffer required in the device varies according to the cable length. The PCI CD/CDa may produce four or more words of valid data after DNR is presented to the input pins.                                                                                                                                                              |  |

#### Timing

The clock and data output timing is specified at the pins of the PCI CD/CDa connector.

#### Table 2. Timing Specifications

|                                  | PCI CD-20  | PCI CD-60     | PCI CDa LVDS                | PCI CDa RS-422           |

|----------------------------------|------------|---------------|-----------------------------|--------------------------|

| Clock frequency                  | 10 MHz     | 30 MHz        | 40 MHz, or as<br>programmed | 10 MHz, or as programmed |

| Clock duty cycle                 | 50% ±10 ns | $50\%\pm5$ ns | $50\% \pm 5 \text{ ns}$     | $50\%\pm5$ ns            |

| Input minimum set-up time        | 20 ns      | 5 ns          | 5 ns                        | 20 ns                    |

| Input minimum hold time          | 25 ns      | 6 ns          | 6 ns                        | 25 ns                    |

| Output maximum propagation delay | 20 ns      | 10 ns         | 10 ns                       | 20 ns                    |

Figure 4 shows the PCI CD/CDa timing.

| Typical DMA data read handshake — input FIFO gets almost full, then empties: |

|------------------------------------------------------------------------------|

| from device RXT L from device DNR L from device IDV H                        |

|                                                                              |

|                                                                              |

| from CD/CDa BNR L                                                            |

| Typical DMA data write handshake — user device needs to hold data out:       |

| from CD/CDa TXT L /                                                          |

| from CD/CDa DAT H(OUT) L(((                                                  |

|                                                                              |

| from device DNR L                                                            |

| Typical data output startup— user device is ready (DNR = false):             |

| from CD/CDa TXT L                                                            |

| from CD/CDa ODV L                                                            |

| from CD/CDa DAT <sup>H</sup> (OUT)                                           |

| from device RXT L                                                            |

Figure 4. PCI CD/CDa Timing

The number of ODV deassertions depends on the frequency of the TXT clock and the PCI Bus response of the host. To minimize or prevent ODV deassertions, align the memory buffer so that data is transferred from a 64-byte boundary. In that case, the first PCI Bus transfer is in burst mode.

#### **Connector Pinouts**

The following pinout diagrams describe the connection from the PCI CD/CDa board to the cable. The board uses a high-density 80-pin I/O connector (EDT part number 012-10026), with a straight-shielded backshell (EDT part number 013-10287) or right-angle backshell (EDT 013-00458).

**NOTE** Do not connect your own circuits to the unused pins, as they may be internally connected.

Table 3 applies to the PCI CD when loaded with either pcd\_src.bit or pcd\_looped.bit, or the PCI CDa when loaded with pcda.bit.

| Pin | Signal                | Pin | Signal               |

|-----|-----------------------|-----|----------------------|

| 1   | ground                | 41  | ground               |

| 2   | ground (spare on CDa) | 42  | ground (spare on CDa |

| 3   | DAT4+                 | 43  | DAT0+                |

| 4   | DAT4–                 | 44  | DAT0-                |

| 5   | DAT5+                 | 45  | DAT1+                |

| 6   | DAT5–                 | 46  | DAT1–                |

| 7   | DAT6+                 | 47  | DAT2+                |

| 8   | DAT6-                 | 48  | DAT2–                |

| 9   | DAT7+                 | 49  | DAT3+                |

| 10  | DAT7–                 | 50  | DAT3–                |

| 11  | DAT12+                | 51  | DAT8+                |

| 12  | DAT12–                | 52  | DAT8–                |

| 13  | DAT13+                | 53  | DAT9+                |

| 14  | DAT13-                | 54  | DAT9–                |

| 15  | DAT14+                | 55  | DAT10+               |

| 16  | DAT14–                | 56  | DAT10-               |

| 17  | DAT15+                | 57  | DAT11+               |

| 18  | DAT15-                | 58  | DAT11–               |

| 19  | spare 0+              | 59  | spare 0–             |

| 20  | +5V                   | 60  | +5V                  |

| 21  | spare 1+              | 61  | spare 1-             |

| 22  | spare 2+              | 62  | spare 2–             |

| 23  | ground                | 63  | ground               |

| 24  | STAT0+                | 64  | RXT+                 |

| 25  | STAT0-                | 65  | RXT–                 |

| 26  | STAT1+                | 66  | IDV+                 |

| 27  | STAT1-                | 67  | IDV-                 |

| 28  | STAT2+                | 68  | DNR+                 |

| 29  | STAT2-                | 69  | DNR-                 |

| 30  | STAT3+                | 70  | reserved+            |

| 31  | STAT3-                | 71  | reserved-            |

| 32  | FUNCT0+               | 72  | SENDT+               |

| 33  | FUNCT0-               | 73  | SENDT-               |

| 34  | FUNCT1+               | 74  | ODV+                 |

| 35  | FUNCT1-               | 75  | ODV-                 |

| 36  | FUNCT2+               | 76  | BNR+                 |

| 37  | FUNCT2-               | 77  | BNR-                 |

| 38  | FUNCT3+               | 78  | TXT+                 |

| 39  | FUNCT3-               | 79  | TXT–                 |

| 40  | ground                | 80  | ground               |

|     |                       |     | 5                    |

| Table 3. PCI CD | (pcd_src.bit, p | ocd_looped.bit), PCI CDa | (pcda.bit) Connector Pinout |

|-----------------|-----------------|--------------------------|-----------------------------|

|-----------------|-----------------|--------------------------|-----------------------------|

# Registers

The PCI CD/CDa has two memory spaces: the memory-mapped registers and the configuration space. Expansion ROM and I/O space are not implemented. Applications can access the PCI CD/CDa registers through the DMA library routines especially <code>edt\_reg\_read()</code> and <code>edt\_reg\_write()</code>, using the symbolic names listed under "Access" for each register.

#### **Configuration Space**

The configuration space is a 64-byte portion of memory required to configure the PCI Local Bus and to handle errors. Its structure is specified by the PCI Local Bus specification. The structure as implemented for the PCI CD/CDa is as shown in Figure 5 and described below.

| Address Bits | 31                  | 16                                                            | 15                               | 0                              |  |  |  |

|--------------|---------------------|---------------------------------------------------------------|----------------------------------|--------------------------------|--|--|--|

| 0x00         | Device ID (CD-20=11 | , CD-60=13, CDa=44)                                           | Vendor ID = 0x123D               |                                |  |  |  |

| 0x04         | Status (see below)  |                                                               | Command (see below)              |                                |  |  |  |

| 0x08         | Class Code = 0x088  | 000                                                           | Revision ID =<br>(will be update |                                |  |  |  |

| 0x0C         | BIST =<br>0x00      | Header Type= 0x00                                             | Latency Timer<br>(set by OS)     | Cache Line Size<br>(set by OS) |  |  |  |

| 0x10         |                     | DMA Base Address Register (set by OS)                         |                                  |                                |  |  |  |

| 0x14         | UI Xilinx M         | UI Xilinx Memory-mapped I/O Base Address Register (set by OS) |                                  |                                |  |  |  |

|              |                     | not implemented                                               |                                  |                                |  |  |  |

| 0x3C         | Max_Lat =<br>0x04   | Min_Gnt =<br>0x04                                             | Interrupt Pin = 0x01             | Interrupt Line<br>(set by OS)  |  |  |  |

Figure 5. Configuration Space Addresses

Values for the status and command fields are shown in Tables 4 and 5. For complete descriptions of the bits in the status and command fields, see the *PCI Local Bus Specification*, available from:

PCI Special Interest Groupwww.pcisig.com

| Bit | Name                       | Value       | Bit | Name                  | Value       |

|-----|----------------------------|-------------|-----|-----------------------|-------------|

| 0–4 | reserved                   | 0           | 10  | DEVSEL Timing         | 0           |

| 5   | 66 MHz Capable             | 1           | 11  | Signaled Target Abort | implemented |

| 6   | UDF Supported              | 0           | 12  | Received Target Abort | implemented |

| 7   | Fast Back-to-back Capable  | 0           | 13  | Received Master Abort | implemented |

| 8   | Data Parity Error Detected | implemented | 14  | Signaled System Error | implemented |

| 9   | DEVSEL Timing              | 1           | 15  | Detected Parity Error | implemented |

#### Table 4. Configuration Space Status Field Values

Table 5. Configuration Space Command Field Values

| Bit | Name                                  | Value       | Bit   | Name                     | Value       |

|-----|---------------------------------------|-------------|-------|--------------------------|-------------|

| 0   | IO Space                              | 0           | 6     | Parity Error Response    | implemented |

| 1   | Memory Space                          | implemented | 7     | Wait Cycle Control       | 0           |

| 2   | Bus Master                            | implemented | 8     | SERR# Enable             | implemented |

| 3   | Special Cycles                        | 0           | 9     | Fast Back-to-back Enable | implemented |

| 4   | Memory Write and<br>Invalidate Enable | 0           | 10–15 | reserved                 | 0           |

| 5   | VGA Palette Snoop                     | 0           |       |                          |             |

#### **PCI Local Bus Addresses**

Figure 6 describes the PCI CD/CDa interface registers in detail. The addresses listed in Figure 6 are offsets from the gate array boot ROM base addresses. This base address is initialized by the PCI Local Bus host operating system at boot time.

**NOTE** The addresses 0x80 and 0x84 are used by the *pciload* utility to update the gate array. User applications must not modify use these registers. Results of running *pciload* do not take effect until after the board has been turned off and then on again.

| Address | Bits | 31      | 16                                           | 15                   | 0              |  |  |  |  |

|---------|------|---------|----------------------------------------------|----------------------|----------------|--|--|--|--|

| 0xCC    |      |         | UI Xilinx data                               |                      |                |  |  |  |  |

| 0xC8    |      |         | PCI interrupt status                         |                      |                |  |  |  |  |

| 0xC4    |      |         | PCI interrupt and U                          | Xilinx configuration |                |  |  |  |  |

| 0x84    |      |         | not used                                     |                      | flash ROM data |  |  |  |  |

| 0x80    |      |         | flash ROM                                    | A address            |                |  |  |  |  |

| 0x20    |      |         | not                                          | used                 |                |  |  |  |  |

| 0x1C    |      |         | scatter-gather DMA next count and control    |                      |                |  |  |  |  |

| 0x18    |      |         | scatter-gather DMA current count and control |                      |                |  |  |  |  |

| 0x14    |      |         | scatter-gather DMA next address              |                      |                |  |  |  |  |

| 0x10    |      |         | scatter-gather DMA current address           |                      |                |  |  |  |  |

| 0x0C    |      |         | main DMA next count and control              |                      |                |  |  |  |  |

| 0x08    |      |         | main DMA current                             | count and control    |                |  |  |  |  |

| 0x04    |      |         | main DMA next address                        |                      |                |  |  |  |  |

| 0x00    |      |         | main DMA current address                     |                      |                |  |  |  |  |

|         |      |         |                                              |                      |                |  |  |  |  |

| Byte    |      | 3       | 2                                            | 1                    | 0              |  |  |  |  |

| Word    |      | <u></u> | 1                                            | 0                    |                |  |  |  |  |

#### Figure 6. PCI Local Bus Addresses

#### Scatter-gather DMA

PCI Direct Memory Access (DMA) devices in Intel-based computers access memory using physical addresses. Because the operating system uses a memory manager to connect the user program to memory, memory pages that appear contiguous to the user program are actually scattered throughout physical memory. Because DMA accesses physical addresses, a DMA read operation must *gather* data from noncontiguous pages, and a write must *scatter* the data back to the appropriate pages. The PCI CD/CDa driver uses information from the operating system to accomplish this. The operating system passes the driver a list of the physical addresses for the user program memory pages. With this information, the driver builds a scatter-gather (SG) table, which the DMA device uses sequentially.

Most other PCI computers offer memory management for the PCI bus as well, so the operating system needs to pass only the address and count for DMA. The addresses appear contiguous to the PCI bus.

The scatter-gather DMA list is stored in memory. The scatter-gather DMA channel copies it as required into the main DMA registers. The format of the DMA list in memory is as follows (illustrated in Figure 7):

- Each page entry takes eight bytes. Therefore, the scatter-gather DMA count is always evenly divisible by eight.

- The first word consists of the 32-bit start address of a memory page.

- The most significant 16 bits of the second word contain control data.

- The least significant 16 bits of the second word contain the count.

Only bit 16 contains control information. When set to one, and when enabled by setting bit 28 of the Scatter-gather DMA Next Count and Control register, this bit causes the main DMA interrupt to be set when the marked page is complete.

#### Figure 7. Scatter-gather DMA List Format

| Bits          | 63 33   | 2 | 31               | 16                 | 0     |

|---------------|---------|---|------------------|--------------------|-------|

| Each<br>entry | address |   | control (unused) | D<br>M<br>A<br>int | count |

All main DMA registers are read-only. Only the corresponding scatter-gather DMA registers must write to them. To initiate a DMA transfer, the driver performs the following general operations:

- 1. It sets up one or more scatter-gather DMA lists in host memory, using the format described above and illustrated in Figure 7.

- 2. It writes the address of the first entry in the list to the Scatter-gather DMA Next Address Register.

- 3. It writes the length of the scatter-gather DMA list to the Scatter-gather DMA Next Count and Control Register, setting the interrupts as you require. Setting bit 29 of this register to 1 starts the DMA.

- 4. If the DMA list is greater than one page, it loads the address of the first entry of the next page and its length, as described in steps 2 and 3, when bit 29 of theScatter-gather DMA Next Count and Control Register is asserted.

#### Main DMA Current Address Register

|     | Size     | 32-bit                                                                                                  |

|-----|----------|---------------------------------------------------------------------------------------------------------|

|     | I/O      | read-only                                                                                               |

|     | Address  | 0x00                                                                                                    |

|     | Access   | EDT_DMA_CUR_ADDR                                                                                        |

|     | Comment  | This register is automatically copied from the main DMA next address register after main DMA completes. |

| Bit | Descript | ion                                                                                                     |

31–0 The address of the current DMA, or the last used address if no DMA is currently active.

#### Main DMA Next Address Register

| Size    | 32-bit                                                                                     |

|---------|--------------------------------------------------------------------------------------------|

| I/O     | read-only                                                                                  |

| Address | 0x04                                                                                       |

| Access  | EDT_DMA_NXT_ADDR                                                                           |

| Comment | The scatter-gather DMA fills this register when required from the scatter-gather DMA list. |

#### Bit Description

31–0 Read the starting address of the next DMA.

#### Main DMA Current Count and Control Register

|     | Size    |          | 32-bit                                                                                                            |

|-----|---------|----------|-------------------------------------------------------------------------------------------------------------------|

|     | I/O     |          | read-only                                                                                                         |

|     | Address |          | 0x08                                                                                                              |

|     | Access  |          | EDT_DMA_CUR_CNT                                                                                                   |

|     | Comme   | nt       | This register is automatically copied from the main DMA next count and control register after main DMA completes. |

| Bit |         | Descript | ion                                                                                                               |

| 31- | 16      | Read-onl | y versions of bits 31–16 of the Scatter-gather DMA current count and control register.                            |

#### 15–0 The number of words still to be transferred in the current DMA.

#### Main DMA Next Count and Control Register

| Size        | 32-bit                                                                                     |

|-------------|--------------------------------------------------------------------------------------------|

| I/O         | read-only                                                                                  |

| Address     | 0x0C                                                                                       |

| Access      | EDT_DMA_NXT_CNT                                                                            |

| Comment     | The scatter-gather DMA fills this register when required from the scatter-gather DMA list. |

| Description |                                                                                            |

#### Bit Description

| 31-16 | Read-only | versions | of bits | 31–16 o | of the So | catter-gather | DMA next | count and control register | • |

|-------|-----------|----------|---------|---------|-----------|---------------|----------|----------------------------|---|

|       |           |          |         |         |           |               |          |                            |   |

15–0 The number of words still to be transferred in the current DMA.

#### Scatter-gather DMA Current Address Register

|     | Size     | 32-bit                                                                                                                                                            |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | I/O      | read-only                                                                                                                                                         |

|     | Address  | 0x10                                                                                                                                                              |

|     | Access   | EDT_SG_CUR_ADDR                                                                                                                                                   |

|     | Comment  | This register is automatically copied from the scatter-gather DMA next address register when that register is valid and the current scatter-gather DMA completes. |

| Bit | Descript | ion                                                                                                                                                               |

31–0 The address of the current DMA, or the last used address if no DMA is currently active.

#### Scatter-gather DMA Next Address Register

| Size    | 32-bit                                                                                  |

|---------|-----------------------------------------------------------------------------------------|

| I/O     | read-write                                                                              |

| Address | 0x14                                                                                    |

| Access  | EDT_SG_NXT_ADDR                                                                         |

| Comment | The driver software writes this register as described in step 2 of the list on page 21. |

#### Bit Description

15–0

31–0 The starting address of the next DMA.

#### Scatter-gather DMA Current Count and Control Register

|      | Size    |          | 32-bit                                                                               |

|------|---------|----------|--------------------------------------------------------------------------------------|