# **PCI 11W User's Guide**

**Revision: 02 March 2010**

**EDT Public** Document Number: 008-00907-02 Revision: 02 - March 2010 Template: edt.dot

**EDT**

# **Control Information**

| Control Item      | Details              |

|-------------------|----------------------|

| Document Owner    | Mark Mason           |

| Information Label | EDT Public           |

| Supersedes        | None                 |

| File Location     | frm:/pci11w/p11w.doc |

| Document Number   | 008-00907-00         |

# **Revision History**

| Rev.      | Date        | Revision Description                                                      | Ву |

|-----------|-------------|---------------------------------------------------------------------------|----|

| 02        | 2010 Mar 04 | P. 6: Under "Testing," para. 2 – Corrected loop kit part number to "016". | РΗ |

| Draft (A) | 2004 Feb 04 | Convert from FrameMaker to Word; update pciload section                   | SV |

**EDT Public** Document Number: 008-00907-02 Template: edt.dot Page 2

EDT

The information in this document is subject to change without notice and does not represent a commitment on the part of Engineering Design Team, Inc. The software described in this document is furnished under a license agreement or nondisclosure agreement. The software may be used or copied only in accordance with the terms of the agreement.

Engineering Design Team, Inc. ("EDT"), makes no warranties, express or implied, including without limitation the implied warranties of merchantibility and fitness for a particular purpose, regarding the software described in this document ("the software"). EDT does not warrant, guarantee, or make any representations regarding the use or the results of the use of the software in terms of its correctness, accuracy, reliability, currentness, or otherwise. The entire risk as to the results and performance of the software is assumed by you. The exclusion of implied warranties is not permitted by some jurisdictions. The above exclusion may not apply to you.

In no event will EDT, its directors, officers, employees, or agents be liable to you for any consequential, incidental, or indirect damages (including damages for loss of business profits, business interruption, loss of business information, and the like) arising out of the use or inability to use the software even if EDT has been advised of the possibility of such damages. Because some jurisdictions do not allow the exclusion or limitation of liability for consequential or incidental damages, the above limitations may not apply to you. EDT's liability to you for actual damages for any cause whatsoever, and regardless of the form of the action (whether in contract, tort [including negligence], product liability or otherwise), will be limited to \$50.

No part of this manual may be reproduced or transmitted in any form or by any means, electronic or mechanical, without the express written agreement of Engineering Design Team, Inc.

© Copyright Engineering Design Team, Inc. 1997–2004. All rights reserved.

Sun, SunOS, SBus, SPARC, and SPARCstation are trademarks of Sun Microsystems, Incorporated.

Windows NT/2000/XP is a registered trademark of Microsoft Corporation.

Intel and Pentium are registered trademarks of Intel Corporation.

UNIX is a registered trademark of X/Open Company, Ltd.

OPEN LOOK is a registered trademark of UNIX System Laboratories, Inc.

Red Hat is a trademark of Red Hat Software, Inc.

IRex is a trademark of Silicon Graphics, Inc.

AIX is a registered trademark of International Business Machines Corporation.

Xilinx is a registered trademark of Xilinx, Inc.

Kodak is a trademark of Eastman Kodak Company.

The software described in this manual is based in part on the work of the independent JPEG Group.

EDT and Engineering Design Team are trademarks of Engineering Design Team, Inc.

**EDT Public** Document Number: 008-00907-02 Revision: 02 - March 2010 Template: edt.dot

# **Contents**

| Overview                                             | 5  |

|------------------------------------------------------|----|

| After Installing Testing                             |    |

| Building the Sample Programs                         |    |

| Uninstalling                                         |    |

| Upgrading the Firmware                               |    |

| Real-time Input and Output                           | 10 |

| Elements of EDT Interface Applications               |    |

| DMA Library Routines                                 |    |

| EDT Message Handler Library                          |    |

| Message Definitions                                  |    |

| Files                                                | 49 |

| Hardware                                             | 57 |

| PCI Local Bus Interface                              | 57 |

| FIFO                                                 |    |

| Device Interface                                     |    |

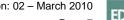

| Logic Levels                                         | 57 |

| Signals                                              | 59 |

| Synchronous Control Signals                          | 61 |

| Handshake Signals                                    |    |

| Asynchronous Control Signals                         |    |

| Unimplemented DR11W Signals                          |    |

| Timing                                               | 63 |

| Registers                                            | 64 |

| Configuration Space                                  | 64 |

| PCI Local Bus Addresses                              |    |

| Scatter-gather DMA                                   |    |

| Performing DMA                                       |    |

| Flash ROM Access Registers  Device Control Registers |    |

| <u> </u>                                             |    |

| Specifications                                       | 78 |

| Poforoncos                                           | 70 |

**EDT Public**

Template: edt.dot

# **Overview**

The PCI 11W is a single-slot, 16-bit parallel input/output interface for PCI local bus-based computer systems. The external interface conforms to the DR11W standard of Digital Equipment Corporation. The PCI 11W features 128 bytes of FIFO storage in each direction and can support continuous data rates of up to 8 MB per second. The board also includes diagnostic capability.

The PCI 11W supports scatter-gather Direct Memory Access (DMA) in hardware, adapting to the memory management model of the host architecture. It includes a software driver and software library, enabling applications to access the PCI 11W and transfer data continuously or in bursts across the PCI 11W interface using standard library calls.

The PCI 11W supports a high-speed block mode as well as all standard DR11W protocols. In this block mode, the PCI 11W transfers data from the PCI Local Bus memory with burst transfers, using FIFO memory on the PCI 11W to buffer the transfer. This capability is useful if your application requires high data transfer rates and does not change direction in mid-block.

The PCI 11W also allows link mode applications, in which one PCI 11W communicates with another or with a DR11W.

Test the PCI 11W by installing an optional loopback connector and executing the PCI 11W diagnostics. A diagnostic program is included with the standard PCI 11W software. The loopback connector kit is available separately. Contact Engineering Design Team or your distributor for further information.

A high-density connector attaches the PCI 11W device to the device cable supplied with the interface. The other end of the cable terminates in two standard DR11W 40-pin connectors. High-density connectors terminate both ends of a PCI 11W-to-PCI 11W interface.

This manual describes the operation of the PCI 11W with UNIX-based and Windows NT operating systems.

Document Number: 008-00907-02 EDT Public Revision: 02 – March 2010

# **After Installing**

After installing the PCI 11W, test the board and build the sample programs, if you wish. Instructions for uninstalling the software and upgrading the firmware are also provided if necessary.

# **Testing**

You can perform diagnostics on the PCI 11W by installing an optional loopback connector and executing the looptest.c diagnostic program included with the standard PCI 11W software. The diagnostic program requires that the PCI 11W driver be installed.

To test the PCI 11W, loop output data from the host back panel or the end of the device cable back to the input. The optional EDT PCI 11W Loopback Kit, part number 016-00067, provides test connectors for both loopback configurations. The loopback kit contains complete instructions for the PCI 11W loopback diagnostics.

The diagnostic program looptest.c, used in conjunction with the loopback test connectors, performs the tests described in the table below. To install the program, at the command prompt, enter:

```

make looptest

```

Use looptest with the following command-line arguments:

| looptest    | [-u n] [-c n                                                                                                               | n] [-b n] [-e] [-t [psfklbi]] loopcount                                                                                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| -u <i>n</i> | The device number of the board to test: use 0 for the first PCI 11W board, 1 for the second, etc. The default device is 0. |                                                                                                                                          |

| -c n        | Sets how many                                                                                                              | words to write for loopback data test. The default is 0xFFFF.                                                                            |

| -b <i>n</i> | Sets how many                                                                                                              | blocks to write for DMA test. The default is 1000.                                                                                       |

| -e          | Prints first misco                                                                                                         | ompared word only.                                                                                                                       |

| -t          | p<br>s<br>f<br>k<br>l<br>b                                                                                                 | est to perform (the default is all): program I/O swap function/status bits input/ouput skew loopback data block loopback interrupt event |

loopcount How many times to run the test. Zero means run until explicitly halted.

| Test Name          | Test Operation Performed                                                                                                                                              |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Loopback Data Test | Wrtie successive values from 0 to 0xFFFF (or other value, if specified with -c argument), then read each word and compare the expected values with the actual values. |

| Swap Test          | With the SWAP bit set, write and read walking ones and zeroes. This test exercises different data paths in the PCI 11W.                                               |

**EDT Public** Document Number: 008-00907-02 Revision: 02 - March 2010 Template: edt.dot

| Block Loopback            | Write 1000 blocks (or other value, if specified with –b argument) of 0x1F000 words, then read back the value of the last word in each block, comparing the actual value with the expected value. |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function/Status Bits      | Output all function bits, and compare the reported function bits in the Status Register with the looped-back status bits.                                                                        |

| ATTN event from pulsed F2 | Set an event interrupt function on ATTN, then pulse FNCT2 (which loops back to ATTN), and check for occurrence of the event.                                                                     |

| Program I/O               | Writes to data register without DMA and compares value read to value written, to ensure correctness.                                                                                             |

| Input and Output Skew     | Writes values to the input and output skew bits of the configuration register to ascertain the input and output skew are functioning correctly.                                                  |

See the "Signals" section on page 59 and the "Registers" section on page 64 for more information.

# **Building the Sample Programs**

# **UNIX-based Systems**

To build any of the example programs on UNIX-based systems, cd to /opt/EDTp11w and enter the command:

make program name

where *file* is the name of the example program you wish to install.

To build and install all the example programs, enter the command:

make

Outcome: All example programs display a message that explains their usage when you enter their names without parameters.

## Windows NT Systems

To build any of the example programs on Windows NT systems:

- 1. Run pcill Utilities.

- 2. Enter the command:

```

nmake program.exe

```

where *file* is the name of the example program you wish to build.

To build and install all the example programs, simply enter the command:

nmake

Outcome: All example programs display a message that explains their usage when you enter their names without parameters.

**Note:** You can also build the sample programs by setting up a project in Windows Visual C++. Contact EDT for instructions.

# Uninstalling

# **Solaris Systems**

To remove the PCI 11W driver on Solaris systems:

- 1. Become root or superuser.

- 2. Enter:

```

pkgrm EDTp11w

```

For further details, consult your operating system documentation, or call Engineering Design Team.

# **Linux Systems**

To remove the PCI 11W driver on Linux systems, enter:

```

cd /opt/EDTp11w

make unload

cd /

rm -rf /opt/EDTp11w

```

# **Windows Systems**

To remove the PCI 11W toolkit on Windows systems, use the Windows Add/Remove utility. For further details, consult your Windows documentation.

You can always get the most recent update of the software from our web site, www.edt.com. See the document titled Contact Us.

# Upgrading the Firmware

Field upgrades to the PCI firmware may occasionally be necessary when upgrading to a new device driver.

The Xilinx file is downloaded to the board's PCI interface Xilinx PROM using the *pciload* program:

- 1. Navigate to the directory in which you installed the driver (for UNIX-based systems, usually /opt/EDTp11w; for Windows, usually  $C: \setminus EDT \setminus p11w$ ).

- 2. At the prompt, enter:

```

pciload verify

```

This will compare the current PCI Xilinx file in the package with what is currently on the board's PROM.

Note: If more than one board is installed on a system, use the following, where N is the board unit number:

```

pciload -u N verify

```

Outcome: Dates and revision numbers of the PROM and File ID will be displayed. If these numbers match, there is no need for a field upgrade. If they differ, upgrade the flash PROM as follows:

At the prompt, enter:

```

pciload update

```

b. Shut down the operating system and turn the host computer off and then back on again. The board reloads firmware from flash ROM only during power-up. Therefore, after running pciload, the new bit file is not in the Xilinx until the system has been power-cycled; simply rebooting is not adequate.

To just see what boards are in the system, run pciload without any arguments:

pciload

To see other pciload options, run:

pciload help

Document Number: 008-00907-02 **EDT Public** Revision: 02 - March 2010 Template: edt.dot

# **Real-time Input and Output**

The PCI 11W device driver can perform two kinds of DMA transfers: continuous and noncontinuous.

To perform continuous transfers, use ring buffers. The ring buffers are a set of buffers that applications can access continuously, reading and writing as required. When the last buffer in the set has been accessed, the application then cycles back to the first buffer. See

edt\_configure\_ring\_buffers for a complete description of the ring buffer parameters that can be configured. See the sample programs simple\_getdata.c and simple\_putdata.c distributed with the driver for examples of using the ring buffers.

For noncontinuous transfers, the driver uses DMA system calls read and write. Each read and write system call performs a single, noncontinuous DMA transfer.

**Note:** For portability, use the library calls edt\_reg\_read, edt\_reg\_write, edt\_reg\_or, or edt\_reg\_and to read or write the hardware registers rather than ioctls.

# Elements of EDT Interface Applications

Applications for performing continuous transfers typically include the following elements:

```

#include "edtinc.h"

main()

EdtDev *edt_p = edt_open("pcd", 0);

char *buf_ptr; int outfd = open("outfile", 1);

/* Configure a ring buffer with four 1MB buffers */

edt_configure_ring_buffers(edt_p, 1024*1024, 4, EDT_READ, NULL);

/* start 4 buffers*/

edt start buffers(edt p, 4);

/* This loop will capture data indefinitely, but the write()

* (or whatever processing on the data) must be able to keep up.

while ((buf_ptr = edt_wait_for_buffers(edt_p, 1)) != NULL)

write(outfd, buf_ptr, 1024*1024) ;

edt_start_buffers(edt_p, 1) ;

edt_close(edt_p) ;

```

Applications for performing noncontinuous transfers typically include the following elements. This example opens a specific DMA channel with edt open channel, assuming that a multi-channel Xilinx firmware file has been loaded:

```

#include "edtinc.h"

main()

EdtDev *edt_p = edt_open_channel("pcd", 1, 2);

char buf[1024] ;

int numbytes, outfd = open("outfile", 1);

```

Document Number: 008-00907-02 **EDT Public** Revision: 02 - March 2010 Template: edt.dot Page 10

```

/*

* Because read()s are noncontinuous, unless is there hardware

* handshaking there will be gaps in the data between each read().

*/

while ((numbytes = edt_read(edt_p, buf, 1024)) > 0)

write(outfd, buf, numbytes);

edt_close(edt_p);

}

```

You can use ring buffer mode for real-time data capture using a small number of buffers (usually four of 1 MB) configured in a round-robin data FIFO. During capture, the application must be able to transfer or process the data before data acquisition wraps around and overwrites the buffer currently being processed.

The example below shows real-time data capture using ring buffers, although it includes no error checking. In this example, process\_data(bufptr) must execute in the same amount of time it takes DMA to fill a single buffer or faster.

```

#include "edtinc.h"

main()

EdtDev *edt_p = edt_open("pcd", 0);

/* Configure four 1 MB buffers:

* one for DMA

* one for the second DMA register on most EDT boards

* one for "process_data(bufptr)" to work on

* one to keep DMA away from "process_data()"

edt_configure_ring_buffers(edt_p, 1*1024*1024, 4, EDT_READ, NULL);

edt_start_buffers(edt_p, 4); /* start 4 buffers */

for (;;)

char *bufptr ;

/* Wait for each buffer to complete, then process it.

* The driver continues DMA concurrently with processing.

bufptr = edt_wait_for_buffers(edt_p, 1) ;

process_data(bufptr) ;

edt_start_buffers(edt_p, 1) ;

}

}

```

Check compiler options in the EDT-provided make files.

Document Number: 008-00907-02

# **DMA Library Routines**

The DMA library provides a set of consistent routines across many of the EDT products, with simple yet powerful ring-buffered DMA capabilities. The following table lists the general DMA library routines, described in an order corresponding roughly to their general usefulness.

| Routine                     | Description                                                                                                               |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Startup/Shutdown            |                                                                                                                           |

| edt_open                    | Opens the EDT Product for application access.                                                                             |

| edt_open_channel            | Opens a specific channel on the EDT Product for application access.                                                       |

| edt_close                   | Terminates access to the EDT Product and releases resources.                                                              |

| edt_parse_unit              | Parses an EDT device name string.                                                                                         |

| Input/Output                |                                                                                                                           |

| edt_read                    | Single, application-level buffer read from the EDT Product.                                                               |

| edt_write                   | Single, application-level buffer write to the EDT Product.                                                                |

| edt_start_buffers           | Begins DMA transfer from or to specified number of buffers.                                                               |

| edt_stop_buffers            | Stops DMA transfer after the current buffer(s) complete(s).                                                               |

| edt_check_for_buffers       | Checks whether the specified number of buffers have completed without blocking.                                           |

| edt_done_count              | Returns absolute (cumulative) number of completed buffers.                                                                |

| edt_get_todo                | Gets the number of buffers that the driver has been told to acquire.                                                      |

| edt_wait_for_buffers        | Blocks until the specified number of buffers have completed.                                                              |

| edt_wait_for_next_buffer    | Waits for the next buffer that completes DMA.                                                                             |

| edt_wait_buffers_timed      | Blocks until the specified number of buffers have completed; returns a pointer to the time that the last buffer finished. |

| edt_next_writebuf           | Returns a pointer to the next buffer scheduled for output DMA.                                                            |

| edt_set_buffer              | Sets which buffer should be started next.                                                                                 |

| edt_set_buffer_size         | Used to change the size or direction of one of the ring buffers.                                                          |

| edt_last_buffer             | Waits for the last buffer that has been transferred.                                                                      |

| edt_last_buffer_timed       | Like edt_last_buffer but also returns the time at which the dma was complete on this buffer.                              |

| edt_configure_ring_buffers  | Configures the ring buffers.                                                                                              |

| edt_buffer_addresses        | Returns an array of addresses referencing the ring buffers.                                                               |

| edt_disable_ring_buffers    | Stops DMA transfer, disables ring buffers and releases resources.                                                         |

| edt_ring_buffer_overrun     | Detects ring buffer overrun which may have corrupted data.                                                                |

| edt_reset_ring_buffers      | Stops DMA in progress and resets the ring buffers.                                                                        |

| edt_configure_block_buffers | Configures ring buffers using a contiguous block of memory.                                                               |

| edt_startdma_action         | Specifies when to perform the action at the start of a dma transfer as set by edt_startdma_reg().                         |

| edt_enddma_action           | Specifies when to perform the action at the end of a dma transfer                                                         |

Document Number: 008-00907-02 **EDT Public** Revision: 02 - March 2010 Template: edt.dot

Template: edt.dot

| Routine                  | Description                                                                                                                                  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Koutine                  | as set by edt_ednddma_reg().                                                                                                                 |

| edt_startdma_reg         | Specifies the register and value to use at the start of dma, as set by edt_startdma_action().                                                |

| edt_abort_dma            | Cancels the current DMA, resets pointers to the current buffer.                                                                              |

| edt_ablort_current_dma   | Cancels the current DMA, moves pointers to the next buffer.                                                                                  |

| edt_get_bytecount        | Returns the number of bytes transferred.                                                                                                     |

| edt_timeouts             | Returns the cumulative number of timeouts since the device was opened.                                                                       |

| edt_get_timeout_count    | Returns the number of bytes transferred as of the last timeout.                                                                              |

| edt_set_timeout_action   | Sets the driver behavior on a timeout.                                                                                                       |

| edt_get_timeout_goodbits | Returns the number of bits from the remote device since the last timeout.                                                                    |

| edt_do_timeout           | Causes the driver to perform the same actions as it would on a timeout (causing partially filled fifos to be flushed and dma to be aborted). |

| edt_get_rtimeout         | Gets the DMA read timeout period.                                                                                                            |

| edt_set_rtimeout         | Sets how long to wait for a DMA read to complete, before returning.                                                                          |

| edt_get_wtimeout         | Gets the DMA write timeout period.                                                                                                           |

| edt_set_wtimeout         | Sets how long to wait for a DMA write to complete, before returning.                                                                         |

| edt_get_timestamp        | Gets the seconds and microseconds timestamp of dma completion on the buffer specified by bufnum.                                             |

| edt_get_reftime          | Gets the seconds and mircroseconds timestamp in the same format as the buffer_timed function.                                                |

| edt_ref_tmstamp          | Used for debugging. Able to see a history with setdebug -g with an application defined event in the same timeline as driver events.          |

| edt_get_burst_enable     | Returns a value indicating whether PCI Bus burst transfers are enabled during DMA.                                                           |

| edt_set_burst_enable     | Turns on or off PCI Bus burst transfers during DMA.                                                                                          |

| edt_get_firstflush       | Returns the value set by edt_set_firstflush(). This is an obsolete function.                                                                 |

| edt_set_firstflush       | Tells whether and when to flush FIFOs before DMA.                                                                                            |

| edt_flush_fifo           | Flushes the EDT Product FIFOs.                                                                                                               |

| edt_get_goodbits         | Returns the number of bits from the remote device.                                                                                           |

| Control                  |                                                                                                                                              |

| edt_set_event_func       | Defines a function to call when an event occurs.                                                                                             |

| edt_remove_event_func    | Removes a previously set event function.                                                                                                     |

| edt_reg_read             | Reads the contents of the specified EDT Product register.                                                                                    |

| edt_reg_write            | Writes a value to the specified EDT Product register.                                                                                        |

| edt_reg_and              | ANDs the value provided with the value of the specified EDT Product register.                                                                |

Document Number: 008-00907-02 EDT Public Revision: 02 – March 2010

EDT

| Routine               | Description                                                                                         |

|-----------------------|-----------------------------------------------------------------------------------------------------|

| edt_reg_or            | ORs the value provided with the value of the specified EDT Product register.                        |

| edt_get_foicount      | Returns the number of RCI modules connected to the EDT FOI (fiber optic interface) board.           |

| edt_set_foiunit       | Sets which RCI unit to address with subsequent serial and register read/write functions.            |

| edt_intfc_write       | A convenience routine, partly for backward compatability, to access the XILINX interface registers. |

| edt_intfc_write_short | A convenience routine, partly for backward compatability, to access the XILINX interface registers. |

| edt_intfc_write_32    | A convenience routine, partly for backward compatability, to access the XILINX interface registers. |

| Utility               |                                                                                                     |

| edt_msleep            | Sleep for the specified number of microseconds.                                                     |

| edt_alloc             | Allocate page-aligned memory in a system-independent way.                                           |

| edt_free              | Free the memory allocated with edt_alloc.                                                           |

| edt_perror            | Prints a system error message in case of error.                                                     |

| edt_errno             | Returns an operating system-dependent error number.                                                 |

| edt_access            | Determines file access independent of operating system.                                             |

| edt_get_bitpath       | Obtains pathname to the currently loaded interface bitfile from the driver.                         |

# edt\_open

# Description

Opens the specified EDT Product and sets up the device handle.

# **Syntax**

```

#include "edtinc.h"

EdtDev *edt_open(char *devname, int unit);

```

## **Arguments**

devname a string with the name of the EDT Product board. For example, "edt".

unit specifies the device unit number

# Return

A handle of type (EdtDev \*), or NULL if error. (The structure(EdtDev \*) is defined in libedt.h.) If an error occurs, check the error global variable for the error number. The device name for the EDT Product is "edt". Once opened, the device handle may be used to perform I/O using edt\_read(), edt\_write(), edt\_configure\_ring\_buffers(), and other input-output library calls.

Document Number: 008-00907-02 **EDT Public** Revision: 02 – March 2010 Template: edt.dot Page 14

# edt\_open\_channel

# Description

Opens a specific DMA channel on the specified EDT Product, when multiple channels are supported by the Xilinx firmware, and sets up the device handle. Use edt\_close() to close the channel.

# **Syntax**

```

#include "edtinc.h"

EdtDev *edt_open_channel(char *devname, int unit, int channel) ;

```

# **Arguments**

devname a string with the name of the EDT Product board. For example, "edt".

unit specifies the device unit number

channel specifies the DMA channel number counting from zero

#### Return

A handle of type (EdtDev \*), or NULL if error. (The structure(EdtDev \*) is defined in libedt.h.) If an error occurs, check the error global variable for the error number. The device name for the EDT Product is "edt". Once opened, the device handle may be used to perform I/O using edt\_read(), edt\_write(), edt\_configure\_ring\_buffers(), and other input-output library calls.

## edt close

# Description

Shuts down all pending I/O operations, closes the device or channel and frees all driver resources associated with the device handle.

## Syntax

```

#include "edtinc.h"

int edt_close(EdtDev *edt_p);

```

#### **Arguments**

edt\_p device handle returned from *edt\_open* or *edt\_open\_channel*.

#### Return

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

**EDT Public** Document Number: 008-00907-02 Template: edt.dot Page 15

# edt\_parse\_unit

# Description

Parses an EDT device name string. Fills in the name of the device, with the default\_device if specified, or a default determined by the package, and returns a unit number. Designed to facilitate a flexible device/unit command line argument scheme for application programs. Most EDT example/utility programs use this subroutine to allow users to specify either a unit number alone or a device/unit number concatenation.

For example, if you are using a PCI CD, then either xtest -u 0 or xtest -u pcd0 could both be used, since xtest sends the argument to edt parse unit, and the subroutine parses the string to returns the device and unit number separately.

# **Syntax**

```

#include "edtinc.h"

int edt_parse_unit(char *str, char *dev, char *default_dev)

```

# **Arguments**

device name string. Should be either a unit number ("0" - "8") or device/unit str

concantenation ("pcd0," "pcd1," etc.)

dev device string, filled in by the routine. For example, "pcd."

default\_dev device name to use if none is given in the str argument. If NULL, will be filled in

by the default device for the package in use. For example, if the code base is from a

PCI CD package, the default\_dev will be set to "pcd."

#### Return

Unit number or -1 on error. The first device is unit 0.

# See Also

example/utility programs xtest.c, initcam.c, take.c

# edt\_read

## Description

Performs a read on the EDT Product. For those on UNIX systems, the UNIX 2 GB file offset bug is avoided during large amounts of input or output, that is, reading past 231 bytes does not fail. This call is not multibuffering, and no transfer is active when it completes.

# Syntax

```

#include "edtinc.h"

int edt_read(EdtDev *edt_p, void *buf, int size);

```

#### **Arguments**

device handle returned from edt\_open or edt\_open\_channel edt\_p

buf address of buffer to read into

size size of read in bytes

Document Number: 008-00907-02 **EDT Public** Revision: 02 - March 2010 Template: edt.dot Page 16

#### Return

The return value from read, normally the number of bytes read; -1 is returned in case of error. Call edt\_perror() to get the system error message.

#### Note

If using timeouts, call edt\_timeouts after edt\_read returns to see if the number of timeouts has incremented. If it has incremented, call edt\_get\_timeout\_count to get the number of bytes transferred into the buffer. DMA does not automatically continue on to the next buffer, so you need to call edt\_start\_buffers to move on to the next buffer in the ring.

# edt\_write

# Description

Perform a write on the EDT Product. For those on UNIX systems, the UNIX 2 GB file offset bug is avoided during large amounts of input or output; that is, writing past 231 does not fail. This call is not multibuffering, and no transfer is active when it completes.

# Syntax

```

#include "edtinc.h"

int edt_write(EdtDev *edt_p, void *buf, int size);

```

## **Arguments**

edt\_p device handle returned from *edt\_open* or *edt\_open\_channel*

address of buffer to write from buf

size size of write in bytes

#### Return

The return value from write; -1 is returned in case of error. Call edt\_perror() to get the system error message.

#### Note

If using timeouts, call edt\_timeouts after edt\_write returns to see if the number of timeouts has incremented. If it has incremented, call edt get timeout count to get the number of bytes transferred into the buffer. DMA does not automatically continue on to the next buffer, so you need to call edt\_start\_buffers to move on to the next buffer in the ring.

# edt\_start\_buffers

#### Description

Starts DMA to the specified number of buffers. If you supply a number greater than the number of buffers set up, DMA continues looping through the buffers until the total count has been satisfied.

# **Syntax**

```

#include "edtinc.h"

int edt_start_buffers(EdtDev *edt_p, int bufnum);

```

# **Arguments**

device handle returned from edt\_open or edt\_open\_channel edt\_p

Number of buffers to release to the driver for transfer. An argument of 0 bufnum

puts the driver in free running mode, and transfers run continuously

until edt\_stop\_buffers() is called.

#### Return

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

# edt\_stop\_buffers

# Description

Stops DMA transfer after the current buffer has completed. Ring buffer mode remains active, and transfers will be continued by calling edt\_start\_buffers().

## Syntax 5 4 1

```

#include "edtinc.h"

int edt_stop_buffers(EdtDev *edt_p);

```

## **Arguments**

*edt\_p* device handle returned from *edt\_open* or *edt\_open\_channel*

## Return

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

# edt check for buffers

## Description

Checks whether the specified number of buffers have completed without blocking.

## **Syntax**

```

#include "edtinc.h"

void *edt check for buffers(EdtDev *edt p, int count);

```

#### **Arguments**

*edt\_p* device handle returned from *edt\_open* or *edt\_open\_channel*. count number of buffers. Must be 1 or greater. Four is recommended.

#### Return

Returns the address of the ring buffer corresponding to count if it has completed DMA, or NULL if count buffers are not yet complete.

#### Note

If the ring buffer is in free-running mode and the application cannot process data as fast as it is acquired, DMA will wrap around and overwrite the referenced buffer. The application must ensure that the data in the buffer is processed or copied out in time to prevent overrun.

# edt\_done\_count

# Description

Returns the cumulative count of completed buffer transfers in ring buffer mode.

## Syntax

```

#include "edtinc.h"

int edt done count(EdtDev *edt p);

Arguments

device handle returned from edt_open or edt_open_channel.

edt_p

```

#### Return

The number of completed buffer transfers. Completed buffers are numbered consecutively starting with 0 when edt\_configure\_ring\_buffers() is invoked. The index of the ring buffer most recently completed by the driver equals the number returned modulo the number of ring buffers. -1 is returned if ring buffer mode is not configured. If an error occurs, call edt perror() to get the system error message.

# edt\_get\_todo

## Description

Gets the number of buffers that the driver has been told to acquire. This allows an application to know the state of the ring buffers within an interrupt, timeout, or when cleaning up on close. It also allows the application to know how close it is getting behind the acquisition. It is not normally needed.

# Syntax

```

#include "edtinc.h"

uint_t edt_get_todo(EdtDev *edt_p);

```

## **Arguments**

edt\_p device handle returned from *edt\_open* or *edt\_open\_channel*.

## Example

```

int curdone;

int curtodo;

curdone=edt_done_count(pdv_p);

curtodo=edt_get_todo(pdv_p);

/* curtodo--curdone how close the dma is to catching with our

processing */

```

#### Return

Number of buffers started via edt start buffers.

#### See Also

edt\_done\_count(), edt\_start\_buffers(), edt\_wait\_for\_buffers()

Document Number: 008-00907-02 Template: edt.dot Page 19

# edt wait for buffers

# Description

Blocks until the specified number of buffers have completed.

# Syntax

```

#include "edtinc.h"

void *edt wait buffers(EdtDev *edt p, int count);

```

## **Arguments**

device handle returned from edt\_open or edt\_open\_channel edt\_p

How many buffers to block for. Completed buffers are numbered relatively; count

start each call with 1.

#### Return

Address of last completed buffer on success; NULL on error. If an error occurs, call edt\_perror() to get the system error message.

#### Note

If using timeouts, call edt\_timeouts after edt\_wait\_for\_buffers returns to see if the number of timeouts has incremented. If it has incremented, call edt\_get\_timeout\_count to get the number of bytes transferred into the buffer. DMA does not automatically continue on to the next buffer, so you need to call edt\_start\_buffers to move on to the next buffer in the ring.

#### Note

If the ring buffer is in free-running mode and the application cannot process data as fast as it is acquired, DMA will wrap around and overwrite the referenced buffer. The application must ensure that the data in the buffer is processed or copied out in time to prevent overrun.

# edt\_wait\_for\_next\_buffer

## Description

Waits for the next buffer that finishes DMA. Depending on how often this routine is called, buffers that have already completed DMA might be skipped.

# Syntax

```

#include "edtinc.h"

void *edt_wait_for_next_buffer(EdtDev *edt_p) ;

```

# **Arguments**

edt\_p device handle returned from *edt\_open* or *edt\_open\_channel*.

#### Return

Returns a pointer to the buffer, or NULL on failure. If an error occurs, call edt\_perror() to get the system error message.

# edt wait buffers timed

# Description

Blocks until the specified number of buffers have completed with a pointer to the time the last buffer finished.

Document Number: 008-00907-02 **EDT Public** Revision: 02 - March 2010 Template: edt.dot Page 20

# **Syntax**

```

#include "edtinc.h"

void *edt_wait_buffers_timed (EdtDev *edt_p, int count, uint *timep);

```

## **Arguments**

device handle returned from edt\_open or edt\_open\_channel edt\_p

count buffer number for which to block. Completed buffers are numbered

cumulatively starting with 0 when the EDT Product is opened.

timep pointer to an array of two unsigned integers. The first integer is seconds, the

next integer is microseconds representing the system time at which the

buffer completed.

#### Return

Address of last completed buffer on success; NULL on error. If an error occurs, call edt\_perror() to get the system error message.

## Note

If the ring buffer is in free-running mode and the application cannot process data as fast as it is acquired, DMA will wrap around and overwrite the referenced buffer. The application must ensure that the data in the buffer is processed or copied out in time to prevent overrun.

# edt\_next\_writebuf

# Description

Returns a pointer to the next buffer scheduled for output DMA, in order to fill the buffer with data.

#### Syntax 5 4 1

```

#include "edtinc.h"

void *edt_next_writebuf(EdtDev *edt_p) ;

```

## **Arguments**

edt\_p device handle returned from *edt\_open* or *edt\_open\_channel*.

### Return

Returns a pointer to the buffer, or NULL on failure. If an error occurs, call edt\_perror() to get the system error message.

# edt\_set\_buffer

## Description

Sets which buffer should be started next. Usually done to recover after a timeout, interrupt, or error.

# **Arguments**

edt\_p device handle returned from *edt\_open* or *edt\_open\_channel*.

#### Syntax 5 4 1

```

#include "edtinc.h"

void *edt_next_writebuf(EdtDev *edt_p) ;

```

Document Number: 008-00907-02 Template: edt.dot Page 21

## Example

```

u int curdone;

edt_stop_buffers(edt_p);

curdone=edt_done_count(edt_p);

edt_set_buffer(edt_p, 0);

Return

0 on success, -1 on failure.

See Also

edt_stop_buffers(), edt_done_count(), edt_get_todo()

```

# edt\_set\_buffer\_size

# Description

Used to change the size or direction of one of the ring buffers. Almost never used. Mixing directions requires detailed knowledge of the interface since pending preloaded DMA transfers need to be coordinated with the interface fifo direction. For example, a dma write will complete when the data is in the output fifo, but the dma read should not be started until the data is out to the external device. Most applications requiring fast mixed reads/writes have worked out more cleanly using seperate, simultaneous, read and write dma transfers using different dma channels.

# **Arguments**

```

device handle returned from edt_open or edt_open_channel

edt_p

which_buf

index of ring buffer to change

size

size to change it to

direction

write_flag

```

#### **Syntax**

```

#include "edtinc.h"

int edt_set_buffer_size(EdtDev *edt_p, unsigned int which_buf,

unsigned int size, unsigned int write_flag)

```

### Example

```

u int bufnum=3;

u int bsize=1024;

u_int dirflag=EDT_WRITE;

int ret;

ret=edt_set_buffer_size(edt_p, bufnum, bsize, dirflag);

```

# Return

0 on success, -1 on failure.

# See Also

edt\_open\_channel(), redpcd8.c, rd16.c, rdssdio.c, wrssdio.c

Document Number: 008-00907-02 Template: edt.dot Page 22

# edt last buffer

# Description

Waits for the last buffer that has been transferred. This is useful if the application cannot keep up with buffer transfer. If this routine is called for a second time before another buffer has been transferred, it will block waiting for the next transfer to complete.

## **Arguments**

```

device struct returned from edt_open

edt_p

```

nSkipped pointer to an integer which will be filled in with number of buffers skipped,

if any.

# **Syntax**

```

#include "edtinc.h"

unsigned char *edt_last_buffer(EdtDev *edt_p, int *nSkipped)

```

# Example

```

int skipped_bufs;

u_char *buf;

buf=edt_last_buffer(edt_p, &skipped_bufs);

```

#### Return

Address of the image.

#### See Also

edt\_wait\_for\_buffers, edt\_last\_buffer\_timed

# edt\_last\_buffer\_timed

# Description

Like edt\_last\_buffer but also returns the time at which the dma was complete on this buffer. "timep" should point to an array of unsigned integers which will be filled in with the seconds and microseconds of the time the buffer was finished being transferred.

## **Arguments**

```

edt_p

device struct returned from edt_open

timep

pointer to an unsigned integer array

```

## **Syntax**

```

#include "edtinc.h"

unsigned char *edt_last_buffer_timed(EdtDev *edt_p, u_int *timep)

Example

u_int timestamp [2];

u_char *buf;

buf=edt_last_buffer_timed(edt_p, timestamp);

```

#### Return

Address of the image.

#### See Also

edt wait for buffers(), edt last buffer(), edt wait buffers timed

# edt\_configure\_ring\_buffers

# Description

Configures the EDT device ring buffers. Any previous configuration is replaced, and previously allocated buffers are released. Buffers can be allocated and maintained within the EDT device library or within the user application itself.

## Syntax

```

#include "edtinc.h"

int edt_configure_ring_buffers(EdtDev *edt_p, int bufsize, int nbufs,

int data_output, void *bufarray[]);

```

# Arguments

device handle returned from edt\_open or edt\_open\_channel edt\_p

bufsize size of each buffer. For optimal efficiency, allocate a value approximating

> throughput divided by 20: that is, if transfer occurs at 20 MB per second, allocate 1 MB per buffer. Buffers significantly larger or smaller can overuse memory or lock the system up in processing interrupts at this speed.

nbufs number of buffers. Must be 1 or greater. Four is recommended for most

applications.

data\_direction Indicates whether this connection is to be used for input or output. Only one

direction is possible per device or subdevice at any given time:

$EDT_READ = 0$ EDT WRITE = 1

bufarray If NULL, the library will allocate a set of page-aligned ring buffers. If not

> NULL, this argument is an array of pointers to application-allocated buffers; these buffers must match the size and number of buffers specified in this call

and will be used as the ring buffers.

#### Return

0 on success; -1 on error. If all buffers cannot be allocated, none are allocated and an error is returned. Call edt\_perror() to get the system error message.

# edt\_buffer\_addresses

#### Description

Returns an array containing the addresses of the ring buffers.

#### **Syntax**

#include "edtinc.h"

Document Number: 008-00907-02 **EDT Public** Revision: 02 - March 2010 Template: edt.dot

```

void **edt_buffer_addresses(EdtDev *edt_p);

```

## **Arguments**

edt\_p

device handle returned from *edt\_open* or *edt\_open\_channel*.

#### Return

An array of pointers to the ring buffers allocated by the driver or the library. The array is indexed from zero to n-1 where n is the number of ring buffers set in edt\_configure\_ring\_buffers().

# edt\_disable\_ring\_buffers

# Description

Disables the EDT device ring buffers. Pending DMA is cancelled and all buffers are released.

# **Syntax**

```

#include "edtinc.h"

int edt_disable_ring_buffers(EdtDev *edt_p);

```

# **Arguments**

*edt\_p*

device handle returned from *edt\_open* or *edt\_open\_channel*

#### Return

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

# edt\_ring\_buffer\_overrun

# Description

Returns true (1) when DMA has wrapped around the ring buffer and overwritten the buffer which the application is about to access. Returns false (0) otherwise.

# **Syntax**

```

#include "edtinc.h"

int edt ring buffer overrun(EdtDev *edt p);

```

#### **Arguments**

*edt\_p*

device handle returned from *edt\_open* or *edt\_open\_channel*.

#### Return

1 (true) when overrun has occurred, corrupting the current buffer, 0 (false) otherwise.

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

# edt reset ring buffers

## Description

Stops any DMA currently in progress, then resets the ring buffer to start the next DMA at bufnum.

## **Syntax**

#include "edtinc.h"

**EDT Public** Document Number: 008-00907-02 Revision: 02 - March 2010 Template: edt.dot

```

int edt_reset_ring_buffers(EdtDev *edt_p, int bufnum) ;

```

## **Arguments**

edt\_p device handle returned from *edt\_open* or *edt\_open\_channel*.

bufnum The index of the ring buffer at which to start the next DMA. A number larger

than the number of buffers set up sets the current done count to the number

supplied modulo the number of buffers.

#### Return

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

# edt\_configure\_block\_buffers

# Description

Similar to edt\_configure\_ring\_buffers, except that it allocates the ring buffers as a single large block, setting the ring buffer addresses from within that block. This allows reading or writing buffers from/to a file in single chunks larger than the buffer size, which is sometimes considerable more efficient. Buffer sizes are rounded up by PAGE SIZE so that DMA occurs on a page boundary.

## **Syntax**

```

#include "edtinc.h"

```

int edt\_configure\_block\_buffers(EdtDev 8edt\_p, int bufsize, int numbufs, int write\_flag, int header\_size, int header\_before)

# **Arguments**

edt\_p device struct returned from edt\_open

bufsize size of the individual buffers numbufs number of buffers to create

write\_flag 1, if these buffers are set up to go out; 0 otherwise

header\_size if non-zero, additional memory (header\_size bytes) will be allocated for each

buffer for Header data. The loocation of this header space is determined by

the argument header\_before.

header\_before if non-zero, the header space defined by header\_size is placed before the

DMA buffer; otherwise, it comes after the DMA buffer. The value returned

by edt\_wait\_for\_buffers is always the DMA buffer.

#### Return

0 on success, -1 on failure.

### See Also

edt\_configure\_ring\_buffers

Document Number: 008-00907-02 **EDT Public** Template: edt.dot Page 26

# edt startdma action

# Description

Specifies when to perform the action at the start of a dma transfer as specified by edt\_startdma\_reg(). A common use of this is to write to a register which signals an external device that dma has started, to trigger the device to start sending. The default is no dma action. The PDV library uses this function to send a trigger to a camera a the start of dma. This function allows the register write to occur in a critical section with the start of dma and at the same time.

## **Syntax**

```

#include "edtinc.h"

void edt_startdma_action(EdtDev *edt_p, uint_t val);

```

## **Arguments**

```

device struct returned from edt_open

edt_p

val

One of EDT_ACT_NEVER, EDT_ACT_ONCE, or EDT_ACT_ALWAYS

```

# Example

```

edt_startdma_action(edt_p, EDT_ACT_ALWAYS);

edt_startdma_reg(edt_p, PDV_CMD, PDV_ENABLE_GRAB);

```

#### Return

void

#### See Also

```

edt_startdma_reg(), edt_reg_write(), edt_reg_read()

```

# edt enddma action

### Description

Specifies when to perform the action at the end of a dma transfer as specified by edt\_enddma\_reg(). A common use of this is to write to a register which signals an external device that dma is complete, or to change the state of a signal which will be changed at the start of dma, so the external device can look for an edge. The default is no end of dma action. Most applications can set the output signal, if needed, from the application with edt\_reg\_write(). This routine is only needed if the action must happen within microseconds of the end of dma.

#### Svntax

```

#include "edtinc.h"

void edt_enddma_action(EdtDev *edt_p, uint_t val);

```

# **Arguments**

```

edt_p

device struct returned from edt_open

val

One of EDT_ACT_NEVER, EDT_ACT_ONCE, or EDT_ACT_ALWAYS

```

#### Example

```

u int fnct value=0x1;

edt_enddma_action(edt_p, EDT_ACT_ALWAYS);

```

Document Number: 008-00907-02 Template: edt.dot Page 27

```

edt_enddma_reg(edt_p, PCD_FUNCT, fnct_value);

```

#### Return

void

#### See Also

edt\_startdma\_action(), edt\_startdma\_reg(), edt\_reg\_write(), edt\_reg\_read()

# edt\_startdma\_reg

## Description

Sets the register and value to use at the start of dma, as set by edt\_startdma\_action().

# **Syntax**

```

#include "edtinc.h"

void edt_startdma_reg(EdtDev *edt_p, uint_t desc, uint_t val);

```

# **Arguments**

*edt\_p* device struct returned from edt\_open desc

register description of which register to use as in edtreg.h

val value to write

# **Example**

```

edt_startdma_action(edt_p, EDT_ACT_ALWAYS);

edt_startdma_reg(edt_p, PDV_CMD, PDV_ENABLE_GRAB);

```

#### Return

void

#### See Also

edt\_startdma\_action()

# edt\_abort\_dma

# Description

Stops any transfers currently in progress, resets the ring buffer pointers to restart on the current buffer.

# Syntax

```

#include "edtinc.h"

int edt_abort_dma(EdtDev *edt_p);

```

# **Arguments**

*edt\_p* device handle returned from *edt\_open* or *edt\_open\_channel*.

## Return

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

**EDT Public** Document Number: 008-00907-02 Revision: 02 - March 2010 Template: edt.dot

# edt\_abort\_current\_dma

# Description

Stops the current transfers, resets the ring buffer pointers to the next buffer.

# **Syntax**

```

#include "edtinc.h"

int edt abort current dma(EdtDev *edt p);

```

## Arguments

*edt\_p* device handle returned from *edt\_open* or *edt\_open\_channel*.

#### Return

0 on success, -1 on failure

# edt\_get\_bytecount

## Description

Returns the number of bytes transferred since the last call of edt\_open, accurate to the burst size, if burst is enabled.

## **Syntax**

```

#include "edtinc.h"

int edt_get_bytecount(EdtDev *edt_p);

```

# **Arguments**

*edt\_p*

device handle returned from edt\_open or edt\_open\_channel

#### Return

The number of bytes transferred, as described above.

# edt\_timeouts

### Description

Returns the number of read and write timeouts that have occurred since the last call of edt\_open.

## **Syntax**

```

#include "edtinc.h"

int edt_timeouts(EdtDev *edt_p);

```

## **Arguments**

*edt\_p*

device handle returned from *edt\_open* or *edt\_open\_channel*

### Return

The number of read and write timeouts that have occurred since the last call of edt\_open.

# edt\_get\_timeout\_count

# Description

Returns the number of bytes transferred at last timeout.

# Syntax

```

#include "edtinc.h"

int edt get timeout count(EdtDev *edt p);

```

## **Arguments**

device handle returned from edt\_open or edt\_open\_channel edt\_p

#### Return

The number of bytes transferred at last timeout.

# edt\_set\_timeout\_action

# Description

Sets the driver behavior on a timeout.

# **Syntax**

```

#include "edtinc.h"

void edt_set_timeout_action(EdtDev *edt_p, int action);

```

# **Arguments**

edt\_p device handle returned from edt\_open or edt\_open\_channel

action integer configures the any action taken on a timeout. Definitions:

> EDT\_TIMEOUT\_NULL no extra action taken

EDT\_TIMEOUT\_BIT\_STROBE flush any valid bits left in input circuits of

SSDIO.

## Return

No return value.

# edt\_get\_timeout\_goodbits

#### Description

Returns the number of good bits in the last long word of a read buffer after the last timeout. This routine is called after a timeout, if the timeout action is set to EDT\_TIMEOUT\_BIT\_STROBE. (See edt\_set\_timeout\_action on page 30.)

# Syntax

```

#include "edtinc.h"

int edt_get_timeout_goodbits(EdtDev *edt_p);

```

# **Arguments**

*edt\_p* device handle returned from edt\_open or edt\_open\_channel

Document Number: 008-00907-02 Template: edt.dot Page 30

#### Return

Number 0–31 represents the number of good bits in the last 32-bit word of the read buffer associated with the last timeout.

# edt\_do\_timeout

## Description

Causes the driver to perform the same actions as it would on a timeout (causing partially filled fifos to be flushed and dma to be aborted). Used when the application has knowledge that no more data will be sent/accepted. Used when a common timeout cannot be known, such as when acquiring data from a telescope ccd array where the amount of data sent depends on unknown future celestial events. Also used by the library when the operating system can not otherwise wait for an interrupt and timeout at the same time.

## Syntax

```

#include "edtinc.h"

int edt_do_timeout(EdtDev *edt_p)

```

# Arguments

# Example

```

edt_do_timeout(edt_p);

```

#### Return

0 on success, -1 on failure

## See Also

ring buffer discussion

# edt\_get\_rtimeout

#### Description

Gets the current read timeout value: the number of milliseconds to wait for DMA reads to complete before returning.

## **Syntax**

```

#include "edtinc.h"

int edt_get_rtimeout(EdtDev *edt_p);

```

# **Arguments**

edt\_p device handle returned from edt\_open or edt\_open\_channel

### Return

The number of milliseconds in the current read timeout period.

Document Number: 008-00907-02 **EDT Public** Revision: 02 – March 2010 Template: edt.dot Page 31

# edt set rtimeout

# Description

Sets the number of milliseconds for data read calls, such as edt\_read(), to wait for DMA to complete before returning. A value of 0 causes the I/O operation to wait forever—that is, to block on a read. Edt set rtimeout affects edt wait for buffers (see page XX) and edt read (see page XX).

## Syntax

```

#include "edtinc.h"

int edt_set_rtimeout(EdtDev *edt_p, int value);

```

# Arguments

*edt\_p* device handle returned from edt\_open or edt\_open\_channel

The number of milliseconds in the timeout period. value

#### Return

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

# edt\_get\_wtimeout

## Description

Gets the current write timeout value: the number of milliseconds to wait for DMA writes to complete before returning.

# Syntax

```

#include "edtinc.h"

int edt get wtimeout(EdtDev *edt p);

Arguments

edt_p

device handle returned from edt_open or edt_open_channel

```

# Return

The number of milliseconds in the current write timeout period.

# edt set wtimeout

## Description

Sets the number of milliseconds for data write calls, such as edt\_write(), to wait for DMA to complete before returning. A value of 0 causes the I/O operation to wait forever—that is, to block on a write. Edt\_set\_wtimeout affects edt\_wait\_for\_buffers (see page XX) and edt\_write (see page XX).

### **Syntax**

```

#include "edtinc.h"

int edt_set_wtimeout(EdtDev *edt_p, int value);

```

# **Arguments**

device handle returned from edt\_open or edt\_open\_channel edt\_p The number of milliseconds in the timeout period. value

#### Return

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

# edt\_get\_timestamp

# Description

Gets the seconds and microseconds timestamp of when dma was completed on the buffer specified by bufnum. "bufnum" is moded by the number of buffers in the ring buffer, so it can either be an index, or the number of buffers completed.

## **Syntax**

```

#include "edtinc.h"

int edt_get_timestamp(EdtDev *edt_p, u_int *timep, u_int bufnum)

```

## **Arguments**

device struct returned from edt\_open edt\_p timep pointer to an unsigned integer array

bufnum buffer index, or number of buffers completed

# Example

```

int timestamp[2];

u_int bufnum=edt_done_count(edt_p);

edt_get_timestamp(edt_p, timestamp, bufnum);

```

## Return

0 on success, -1 on failure. Fills in timestamp pointed to by timep.

# See Also

edt\_timestamp(), edt\_done\_count(), edt\_wait\_buffers\_timed

# edt\_get\_reftime

#### Description

Gets the seconds and microseconds timestamp in the same format as the buffer\_timed functions. Used for debugging and coordinating dma completion time with other events.

#### Syntax

```

#include "edtinc.h"

int edt_get_reftime(EdtDev *edt_p, u_int *timep)

```

# **Arguments**

edt\_p device struct returned from edt\_open timep pointer to an unsigned integer array

buffer index, or number of buffers completed bufnum

# Example

```

int timestamp[2];

edt_get_regtime(edt_p, timestamp);

```

#### Return

0 on success, -1 on failure. Fills in timestamp pointed to by timep.

#### See Also

edt\_timestamp(), edt\_done\_count(), edt\_wait\_buffers\_timed

# edt\_ref\_tmstamp

## Description

Used for debugging and viewing a history with setdebug -g with an application-defined event in the same timeline as driver events.

# **Syntax**

```

#include "edtinc.h"

int edt_ref_tmstamp(EdtDev *edt_p, u_int val)

```

# **Arguments**

*edt\_p* device struct returned from edt\_open val an arbitrary value meaningful to the application

## Example

```

#define BEFORE_WAIT 0x11212aaaa

#define AFTER_WAIT 0x3344bbbb

u_char *buf;

edt_ref_tmstamp(edt_p, BEFORE_WAIT);

buf=edt_wait_for_buffer(edt_p);

edt_reg_tmstamp(edt_p, AFTER_WAIT);

/* now look at output of setdebug -g */

```

#### Return

0 on success, -1 on failure.

#### See Also

documentation on setdebug

**EDT Public** Document Number: 008-00907-02 Revision: 02 - March 2010 Template: edt.dot

# edt\_get\_burst\_enable

# Description

Returns the value of the burst enable flag, determining whether the DMA master transfers as many words as possible at once, or transfers them one at a time as soon as the data is acquired. Burst transfers are enabled by default to optimize use of the bus. For more information, see edt\_set\_burst\_enable on page 35.

# **Syntax**

```

#include "edtinc.h"

int edt get burst enable(EdtDev *edt p);

Arguments

edt_p

device handle returned from edt_open or edt_open_channel

```

#### Return

A value of 1 if burst transfers are enabled: 0 otherwise.

# edt\_set\_burst\_enable

## Description

Sets the burst enable flag, determining whether the DMA master transfers as many words as possible at once, or transfers them one at a time as soon as the data is acquired. Burst transfers are enabled by default to optimize use of the bus; however, you may wish to disable them if data latency is an issue, or for diagnosing DMA problems.

## Syntax

```

#include "edtinc.h"

void edt_set_burst_enable(EdtDev *edt_p, int onoff);

Arguments

edt_p

device handle returned from edt_open or edt_open_channel

onoff

A value of 1 turns the flag on (the default); 0 turns it off.

```

#### Return

No return value.

# edt\_get\_firstflush

## Description

Returns the value set by edt\_set\_firstflush(). This is an obsolete function that was only used as a kludge to detect EDT\_ACT\_KBS (also obsolete).

# Syntax

```

#include "edtinc.h"

int edt_get_firstflush(EdtDev *edt_p)

```

**EDT Public** Document Number: 008-00907-02 Template: edt.dot Page 35

# **Arguments**

edt\_p device struct returned from edt\_open.

# Example

```

int application_should_already_know_this;

application_should_already_know_this=edt_get_firstflush(edt_p);

```

#### Return

Yes

#### See Also

edt\_set\_firstflush

# edt\_set\_firstflush

# Description

Tells whether and when to flush the FIFOs before DMA transfer. By default, the FIFOs are not flushed. However, certain applications may require flushing before a given DMA transfer, or before each transfer.

## Syntax

```

#include "edtinc.h"

int *edt_set_firstflush(EdtDev *edt_p, int flag) ;

```

# **Arguments**

*edt\_p* device handle returned from edt\_open or edt\_open\_channel. Tells whether and when to flush the FIFOs. Valid values are: flag

> EDT\_ACT\_NEVER don't flush before DMA transfer (default) EDT\_ACT\_ONCE flush before the start of the next DMA transfer EDT\_ACT\_ALWAYS flush before the start of every DMA transfer

#### Return

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

# edt\_flush\_fifo

# Description

Flushes the board's input and output FIFOs, to allow new data transfers to start from a known state.

# Syntax

```

#include "edtinc.h"

void edt_flush_fifo(EdtDev *edt_p);

```

## **Arguments**

edt\_p device handle returned from edt\_open or edt\_open\_channel

#### Return

No return value.

## edt\_get\_goodbits

#### Description

Returns the current number of good bits in the last long word of a read buffer (0 through 31).

## **Syntax**

```

#include "edtinc.h"

int edt_get_goodbits(EdtDev *edt_p);

```

## **Arguments**

edt\_p

device handle returned from edt\_open or edt\_open\_channel

#### Return

Number 0–31 represents the number of good bits in the 32-bit word of the current read buffer.

## edt\_set\_event\_func

## Description

Defines a function to call when an event occurs. Use this routine to send an application-specific function when required; for example, when DMA completes, allowing the application to continue executing until the event of interest occurs.

If you wish to receive notification of one event only, and then disable further event notification, send a final argument of 0 (see the continue parameter described below). This disables event notification at the time of the callback to your function.

#### **Syntax**

```

#include "edtinc.h"

int edt_set_event_func(EdtDev *edt_p, int event, void (*func)(void

*),

void *data, int continue);

```

#### **Arguments**

edt\_p device handle returned from *edt\_open* or *edt\_open\_channel*. event The event that causes the function to be called. Valid events are:

| Event                 | Description                                                                                                   | Board                          |

|-----------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------|

| EDT_PDV_EVENT_ACQUIRE | Image has been acquired;<br>shutter has closed; subject can<br>be moved if necessary; DMA<br>will now restart | PCI DV,<br>PCI DVK,<br>PCI FOI |

| EDT_PDV_EVENT_FVAL    | Frame Valid line is set                                                                                       | PCI DV,<br>PCI DVK             |

| EDT EVENT P16D DINT   | Device interrupt occurred                                                                                     | PCI 16D                        |

**EDT Public** Document Number: 008-00907-02 Revision: 02 - March 2010 Template: edt.dot Page 37

|          | EDT_EVENT_P11W_ATTN                                             | Attention interrupt occurred        | PCI 11W      |

|----------|-----------------------------------------------------------------|-------------------------------------|--------------|

|          | EDT_EVENT_P11W_CNT                                              | Count interrupt occurred            | PCI 11W      |

|          | EDT_EVENT_PCD_STAT1                                             | Interrupt occurred on Status 1 line | PCI CD       |

|          | EDT_EVENT_PCD_STAT2                                             | Interrupt occurred on Status 2 line | PCI CD       |

|          | EDT_EVENT_PCD_STAT3                                             | Interrupt occurred on Status 3 line | PCI CD       |

|          | EDT_EVENT_PCD_STAT4                                             | Interrupt occurred on Status 4 line | PCI CD       |

|          | EDT_EVENT_ENDDMA                                                | DMA has completed                   | ALL          |

| func     | The function you've defined to c                                | all when the event occurs.          |              |

| data     | Pointer to data block (if any) to sedt_p.                       | end to the function as an argume    | ent; usually |

| continue | Flag to enable or disable continuing implied edt_remove_event_f |                                     | 0 causes an  |

|          |                                                                 |                                     |              |

#### Return

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

## edt\_remove\_event\_func

## Description

Removes an event function previously set with edt\_set\_event\_func.

**Note** This routine is implemented on PCI Bus platforms only.

## **Syntax**

```

#include "edtinc.h"

int edt_remove_event_func(EdtDev *edt_p, int event);

```

#### **Arguments**

edt\_p device handle returned from edt\_open or edt\_open\_channel.

event The event that causes the function to be called. Valid events are as listed in

edt\_set\_event\_func on page 37.

#### Return

0 on success; -1 on error. If an error occurs, call edt\_perror() to get the system error message.

Document Number: 008-00907-02 **EDT Public** Revision: 02 – March 2010 Template: edt.dot Page 38

## edt\_reg\_read

## Description

Reads the specified register and returns its value. Use this routine instead of using ioctls.

#### Syntax

```

#include "edtinc.h"

uint edt_reg_read(EdtDev *edt_p, uint address);

```

## **Arguments**

edt\_p device handle returned from edt\_open or edt\_open\_channel