First-in, first-out (FIFO) memory buffers are used to smooth data transmission between different types of data sinks internal to EDT boards. For instance, the FIFO stores information processed by the user interface FPGA until the PCI FPGA retrieves it across the PCI bus. The PCI bus normally sends information in bursts, so the FIFO allows this same information to be sent smoothly.

When acquiring or sending data, flush the FIFO immediately before performing DMA. This also resets the FIFO to an empty state. The following subroutines either flush the FIFO or set it to flush automatically at the start of DMA.

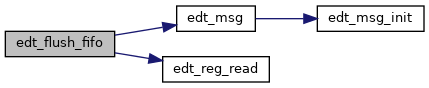

◆ edt_flush_fifo()

| void edt_flush_fifo |

( |

EdtDev |

edt_p | ) |

|

Flush the board's input and output FIFOs to allow new data transfers to start from a known state.

- Parameters

-

| edt_p | The open EDT device handle. |

◆ edt_set_firstflush()

| int edt_set_firstflush |

( |

EdtDev |

edt_p, |

|

|

int |

flag |

|

) |

| |

Specify whether and when to flush the FIFOs before DMA transfer. By default, the FIFOs are not flushed. However, certain applications may require flushing before a given DMA transfer, or before each transfer.

- Parameters

-

| edt_p | The open EDT device handle. |

| flag | Tells whether and when to flush the FIFOs. Valid values are:

EDT_ACT_NEVER don't flush before DMA transfer (default) EDT_ACT_ONCE flush before the start of the next DMA transfer EDT_ACT_ALWAYS flush before the start of every DMA transfer

|

- Returns

- 0 on success; -1 on error.

◆ edt_enable_channels()

| int edt_enable_channels |

( |

EdtDev |

edt_p, |

|

|

u_int |

mask |

|

) |

| |

Set DMA channel enable bits in SSD16_CHEN or SSD16_CHEN32 register.

- Parameters

-

| edt_p | The open EDT device handle. |

| mask | If a bit in this mask is set to 1, the corresponding DMA channel will be enabled. Other channel enable bits will be unaffected. |

- Returns

- 0 on success, -1 on failure

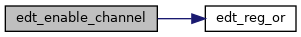

◆ edt_enable_channel()

| int edt_enable_channel |

( |

EdtDev |

edt_p, |

|

|

u_int |

channel |

|

) |

| |

Set DMA channel enable bit in SSD16_CHEN or SSD16_CHEN32 register.

- Parameters

-

| edt_p | The open EDT device handle. |

| channel | Index of the channel to enable. |

- Returns

- 0 on success, -1 on failure

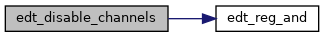

◆ edt_disable_channels()

| int edt_disable_channels |

( |

EdtDev |

edt_p, |

|

|

u_int |

mask |

|

) |

| |

Clear DMA channel enable bits in SSD16_CHEN or SSD16_CHEN32 register.

- Parameters

-

| edt_p | The open EDT device handle. |

| mask | If a bit in this mask is set to 1, the corresponding DMA channel will be disabled. Other channel enable bits will be unaffected. |

- Returns

- 0 on success, -1 on failure

◆ edt_disable_channel()

| int edt_disable_channel |

( |

EdtDev |

edt_p, |

|

|

u_int |

channel |

|

) |

| |

Clear DMA channel enable bit in SSD16_CHEN or SSD16_CHEN32 register.

- Parameters

-

| edt_p | The open EDT device handle. |

| channel | Index of the channel to disable. |

- Returns

- 0 on success, -1 on failure