|

EDT PDV SDK Documentation 6.1.0

|

|

EDT PDV SDK Documentation 6.1.0

|

Functions | |

| void | edt_spi_send_packet (EdtDev edt_p, u_char *cmdbuf) |

| Send a command packet to the msp430 via the SPI; wait for output fifo full but not ACK/NAK reply. More... | |

| u_char | edt_spi_get_byte (EdtDev edt_p) |

| Polls the EDT SPI master for a single byte. More... | |

| u_char | edt_spi_put_byte (EdtDev edt_p, u_char ch) |

| Sends one byte to the EDT SPI master. More... | |

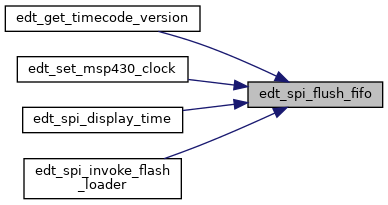

| void | edt_spi_flush_fifo (EdtDev edt_p) |

| Flushes the EDT SPI input and output fifos, discarding all data. More... | |

| char * | edt_spi_putstr (EdtDev edt_p, char *const str) |

| Send a single line of ascii string to the msp430 over SPI. More... | |

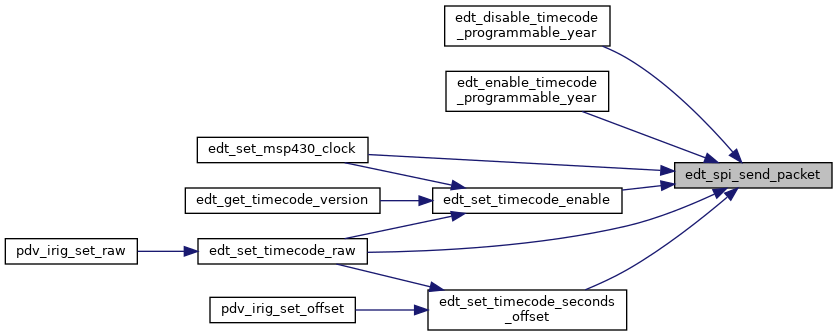

Utility Functions

| void edt_spi_send_packet | ( | EdtDev | edt_p, |

| u_char * | cmdbuf | ||

| ) |

Send a command packet to the msp430 via the SPI; wait for output fifo full but not ACK/NAK reply.

After a packet-start byte is received, call this routine to input the packet and check the CRC.

| edt_p | The EDT open device handle. |

| str | The formatted command buffer to send as a packet. |

Packets to and from the msp430 microcontroller over the SPI bus always start with

#define SPI_PKT_START 0x82 Start of packet byte.

followed by a command buffer, followed by a two-byte command buffer CRC check.

The command buffer consists of the following:

byte 0: Command byte byte 1: Number of data bytes 0 - 60 bytes 2 - 62: Command specific data bytes

Currently supported commands are:

#define SPI_PACKET_LOOP 0 Loop back packet; send back the packet. Data size

0-60 bytes; no ACK/NAK response.

#define SPI_TIMECODE_EN 1 Enable (1) or disable (0) the 1 Hz ascii-hex

timestamp. Data size 1 byte. ACK/NAK response.

#define SPI_CLK_SELECT 2 Select msp430 clock source as internal DCO (0) or

external XIN (1) plus clock rate. ACK/NAK response. Data size 5 bytes; first byte selects internal/external, last 4 bytes is an integer specifying the clock rate in Hz; LS byte first; MS byte last. Currently supported clock rates for DCO (0) are 1, 8, 12 and 16 Mhz. Currently supported clock rate for XIN (1) is 10 Mhz.

#define SPI_TIMECODE_PKT 3 Sent from msp430 to FPGA. Data consists of 4-8

bytes of timecode LSByte first, extended UNIX seconds time format.

The CRC check bytes apply to the command buffer (command, length and data bytes), and is computed as follows where CKL is the low CRC byte, CKH is the high CRC byte, B1 is the Command byte and Bn is the last data byte (derived from Texas Instruments Application Report SLAA089D "Features of the MSP430 Bootstrap Loader"):

CKL = INV [ B1 XOR B3 XOR ... XOR Bn–1 ] CKH = INV [ B2 XOR B4 XOR ... XOR Bn ]

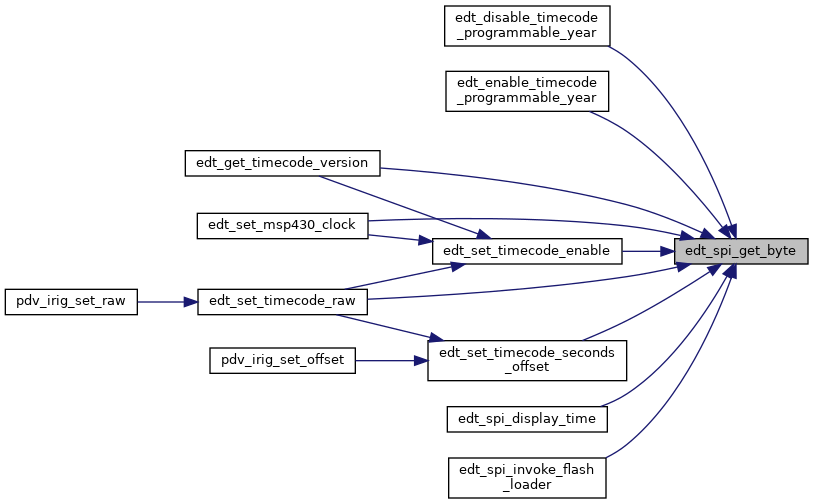

| u_char edt_spi_get_byte | ( | EdtDev | edt_p | ) |

Polls the EDT SPI master for a single byte.

| edt_p | The EDT open device handle. |

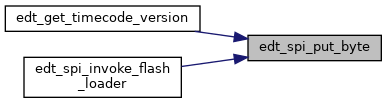

| u_char edt_spi_put_byte | ( | EdtDev | edt_p, |

| u_char | ch | ||

| ) |

Sends one byte to the EDT SPI master.

| edt_p | The EDT open device handle. |

| ch | The byte to send to the SPI master. |

| void edt_spi_flush_fifo | ( | EdtDev | edt_p | ) |

Flushes the EDT SPI input and output fifos, discarding all data.

| edt_p | The EDT open device handle. |

| char * edt_spi_putstr | ( | EdtDev | edt_p, |

| char *const | str | ||

| ) |

Send a single line of ascii string to the msp430 over SPI.

| edt_p | The EDT open device handle. |

| str | The null-terminated string to send to the EDT SPI interface. |