|

EDT PDV SDK Documentation 6.1.0

|

|

EDT PDV SDK Documentation 6.1.0

|

Functions | |

| void | pdv_cls_dump_state (PdvDev pdv_p) |

| Prints the board state to stdout. More... | |

| void | pdv_cls_dump_geometry (PdvDev pdv_p) |

| Prints board geometry only to stdout. More... | |

| int | pdv_cls_set_dep (PdvDev pdv_p) |

Initializes CLS values based on PdvDependent structure in pdv_p. More... | |

| int | pdv_cls_dep_sanity_check (PdvDev pdv_p) |

| Checks for inconsistencies in the configuration completed by pdv_cls_set_dep(). More... | |

| void | pdv_cls_set_size (PdvDev pdv_p, int taps, int depth, int width, int height, int hblank, int totalwidth, int vblank, int totalheight) |

| Set the width and height of the simulator frame. More... | |

| void | pdv_cls_set_line_timing (PdvDev pdv_p, int width, int taps, int Hfvstart, int Hfvend, int Hlvstart, int Hlvend, int Hrvstart, int Hrvend) |

| Set the values for frame valid (FVAL), line valid (LVAL), and read valid (RVAL) timing. More... | |

| void | pdv_cls_set_linescan (PdvDev pdv_p, int state) |

| When set, once the start-of-frame conditions are met, the simulator runs forever, emulating a linescan camera (as if the total vertical active and total vertical count maximum were set to infinity.) More... | |

| void | pdv_cls_set_lvcont (PdvDev pdv_p, int state) |

| Enable/Disable line valid timing during vertical blanking. More... | |

| void | pdv_cls_set_rven (PdvDev pdv_p, int state) |

| Enable/Disable ReadValid Enable (RVEN); if enabled allows image width padding (with dummy data from the Fill register values), to output an image that is wider than the actual image data provided. More... | |

| void | pdv_cls_set_uartloop (PdvDev pdv_p, int state) |

| Enable/Disable UART looping (echo) of serial data; if enabled allows testing of the serial port on an EDT Framegrabber. More... | |

| void | pdv_cls_set_smallok (PdvDev pdv_p, int state) |

| Enable/Disable CLS FIFO for small (less than 16 KB) images. More... | |

| void | pdv_cls_set_intlven (PdvDev pdv_p, int state) |

| Enables or disables four-tap interleaving (the four-tap re-ordering of 8-bit pixel values). More... | |

| void | pdv_cls_set_firstfc (PdvDev pdv_p, int state) |

| Enable/Disable frame count in the first word of each frame. More... | |

| void | pdv_cls_set_datacnt (PdvDev pdv_p, int state) |

| Enable/Disable internal image data generation; allows image data to come from the counters instead of the DMA stream. More... | |

| void | pdv_cls_set_led (PdvDev pdv_p, int state) |

| Controls state of the board's green LED. More... | |

| void | pdv_cls_set_trigsrc (PdvDev pdv_p, int select) |

| Selects which input pins to look at for external trigger; CC1 or CC2. More... | |

| void | pdv_cls_set_trigpol (PdvDev pdv_p, int polarity) |

| Set the trigger polarity. More... | |

| void | pdv_cls_set_trigframe (PdvDev pdv_p, int state) |

| Enable/Disable frame-valid triggering; if enabled CLS waits at the start of each frame until a trigger is detected. More... | |

| void | pdv_cls_set_trigline (PdvDev pdv_p, int state) |

| Enable/Disable line-valid triggering; if enabled CLS waits at the start of each raster until a trigger is detected. More... | |

| void | pdv_cls_sim_start (PdvDev pdv_p) |

| Clear the CFG register including the FIFO_RESET bit (bit 3, 0x08) which clears the FIFO and starts the CLS. More... | |

| void | pdv_cls_sim_stop (PdvDev pdv_p) |

| Set the CFG register FIFO_RESET bit (bit 3, 0x08) which stops the CLS. More... | |

| void | pdv_cls_init_serial (PdvDev pdv_p) |

| Re-intializes and enables the serial communication. More... | |

| void | pdv_cls_set_height (PdvDev pdv_p, int height, int vblank) |

Set the height of outgoing frames, as well as the number of blank lines (vblank) between valid lines. More... | |

| void | pdv_cls_set_width (PdvDev pdv_p, int width, int hblank) |

Set the width of outgoing frames, as well as the number of blank columns (hblank) between valid columns. More... | |

| void | pdv_cls_set_width_lval_rval (PdvDev pdv_p, int width, int hblank, int hlvstart, int hlvend, int hrvstart, int hrvend) |

Set the width of outgoing frames, as well as the number of blank columns (hblank) between valid columns, start and end of both line valid and read valid. More... | |

| void | pdv_cls_set_depth (PdvDev pdv_p, int value) |

| Set the depth of outgoing frames. More... | |

| void | pdv_cls_set_clock (PdvDev pdv_p, double freq) |

| Set the pxiel clock frequency (in MHz). More... | |

| void | pdv_cls_set_fill (PdvDev pdv_p, u_char left, u_char right) |

| Set the left and right fill values when RVEN (pdv_cls_set_rven()) is enabled. More... | |

| void | pdv_cls_set_readvalid (PdvDev pdv_p, u_short HrvStart, u_short HrvEnd) |

| Set the horizontal start and end positions if RVEN (pdv_cls_set_rven()) is enabled. More... | |

| void | pdv_cls_set_dvalid (PdvDev pdv_p, u_char skip, u_char mode) |

| Set the values for Data Valid (DVAL) timing. More... | |

| void | pdv_cls_setup_interleave (PdvDev pdv_p, short tap0start, short tap0delta, short tap1start, short tap1delta, short tap2start, short tap2delta, short tap3start, short tap3delta) |

| Set the start address and delta for each tap. More... | |

| int | pdv_cls_get_vgap (PdvDev pdv_p) |

| Computes the vertical gap (vgap\vblank) value. More... | |

| int | pdv_cls_get_hgap (PdvDev pdv_p) |

| Computes the horizontal gap (hgap/hblank) value. More... | |

| double | pdv_cls_frame_time (PdvDev pdv_p) |

| Computes the frame time in milliseconds. More... | |

The CameraLink Simulator Library provides programming access to the EDT CLS board.

The source code for the library is in clsim_lib.c and clsim_lib.h.

The following applications are also provided:

| void pdv_cls_dump_state | ( | PdvDev | pdv_p | ) |

Prints the board state to stdout.

| pdv_p | The open EDT device handle. |

| void pdv_cls_dump_geometry | ( | PdvDev | pdv_p | ) |

Prints board geometry only to stdout.

| pdv_p | The open EDT device handle. |

| int pdv_cls_set_dep | ( | PdvDev | pdv_p | ) |

Initializes CLS values based on PdvDependent structure in pdv_p.

| pdv_p | The open EDT device handle. |

The structure is normally filled in by clsiminit.

Assumes bitfile is already loaded.

| int pdv_cls_dep_sanity_check | ( | PdvDev | pdv_p | ) |

Checks for inconsistencies in the configuration completed by pdv_cls_set_dep().

| pdv_p | The open EDT device handle. |

Currently this is a stub. In the future it will return a nonzero error code if a problem is found.

| void pdv_cls_set_size | ( | PdvDev | pdv_p, |

| int | taps, | ||

| int | depth, | ||

| int | width, | ||

| int | height, | ||

| int | hblank, | ||

| int | totalwidth, | ||

| int | vblank, | ||

| int | totalheight | ||

| ) |

Set the width and height of the simulator frame.

| pdv_p | The open EDT device handle. |

| taps | Number of clocks per line. |

| depth | Frame depth, in bits of data. |

| width | Frame width; columns or pixels of active data. |

| height | Frame height; lines of active data. |

| hblank | Horizontal blanking, in columns. |

| totalwidth | Total width including horizontal blanking if hblank is zero. |

| vblank | Vertical blanking, in lines. |

| totalwidth | Total number of lines including vertical blanking if vblank is zero. |

There are two ways to set the total width and height including blanking:

hblank is non-zero, the total line width is the sum of width and hblank.totalwidth.Likewise

vblank is non-zero, the number of lines between frame valid is the sum of height and vblank.totalheight.

| void pdv_cls_set_line_timing | ( | PdvDev | pdv_p, |

| int | width, | ||

| int | taps, | ||

| int | Hfvstart, | ||

| int | Hfvend, | ||

| int | Hlvstart, | ||

| int | Hlvend, | ||

| int | Hrvstart, | ||

| int | Hrvend | ||

| ) |

Set the values for frame valid (FVAL), line valid (LVAL), and read valid (RVAL) timing.

| pdv_p | The open EDT device handle. |

| taps | Number of clocks per line. |

| width | Frame width; columns or pixels of active data. |

| Hfvstart | Horizontal FVAL start; column on which the frame signal is valid (high). |

| Hfvend | Horizontal FVAL end; column on which the frame signal is no longer valid (low). |

| Hlvstart | Horizontal LVAL start; column on which the line signal is valid (high). |

| Hlvend | Horizontal LVAL end; column on which the line signal is no longer valid (low). |

| Hrvstart | Horizontal RVAL start; column on which the read signal is valid (high). |

| Hrvend | Horizontal RVAL end; column on which the read signal is no longer valid (low). |

In each case, if the end value is 0, the number of clocks required for width is added to the start value (default 0). So if start and end are 0, defaults are start = 0 and end = width/taps.

| void pdv_cls_set_linescan | ( | PdvDev | pdv_p, |

| int | state | ||

| ) |

When set, once the start-of-frame conditions are met, the simulator runs forever, emulating a linescan camera (as if the total vertical active and total vertical count maximum were set to infinity.)

| pdv_p | The open EDT device handle. |

| state | Enable (1) or disable (0) linescan. |

| void pdv_cls_set_lvcont | ( | PdvDev | pdv_p, |

| int | state | ||

| ) |

Enable/Disable line valid timing during vertical blanking.

| pdv_p | The open EDT device handle. |

| state | Enable (1) or disable (0) continuous line valid. |

When enabled the line valid is asserted continuously with it's normal timing, even during the vertical blanking interval between frames.

When disabled the line valid remains low during vertical blanking.

Default state is disabled (0).

| void pdv_cls_set_rven | ( | PdvDev | pdv_p, |

| int | state | ||

| ) |

Enable/Disable ReadValid Enable (RVEN); if enabled allows image width padding (with dummy data from the Fill register values), to output an image that is wider than the actual image data provided.

| pdv_p | The open EDT device handle. |

| state | Enable (1) or disable (0) ReadValid. |

Read valid is special functionality, not in the Camera Link specification.

When enabled, the start and end margins of each raster are filled with the values from the FillA and FillB registers respectively, the positions of the margins are determined by HrvStart and HrvEnd (Hrv* are set with pdv_cls_set_readvalid().

When disabled, the entire raster is filled with valid data.

| void pdv_cls_set_uartloop | ( | PdvDev | pdv_p, |

| int | state | ||

| ) |

Enable/Disable UART looping (echo) of serial data; if enabled allows testing of the serial port on an EDT Framegrabber.

| pdv_p | The open EDT device handle. |

| state | Enable (1) or disable (0) uart looping. |

| void pdv_cls_set_smallok | ( | PdvDev | pdv_p, |

| int | state | ||

| ) |

Enable/Disable CLS FIFO for small (less than 16 KB) images.

| pdv_p | The open EDT device handle. |

| state | Enable (1) or disable (0) the simulator FIFO. |

When enabled CLS starts DMA when 1 KB of data is in the FIFO, allowing images smaller than 16 KB.

When disabled CLS waits until 16 KB of data is in the FIFO before starting DMA.

Default state is disabled (0).

| void pdv_cls_set_intlven | ( | PdvDev | pdv_p, |

| int | state | ||

| ) |

Enables or disables four-tap interleaving (the four-tap re-ordering of 8-bit pixel values).

| pdv_p | The open EDT device handle. |

| state | Enable (1) or disable (0) interleave. |

See the CLS Users Guide, Appendix A for a complete description of how data is interleaved. For example, 0x60-61 Tap 0 Start through 0xE-6F Tap 3 Delta. Image data destined for the Framegrabber is first passed through an interleaving mechanism to duplicate the data ordering that some cameras exhibit. When interleaving is enabled, rasters are restricted to a maximum of 4096 eight-bit pixels of active image data (DMA plus fill).

Default state is disabled (0).

| void pdv_cls_set_firstfc | ( | PdvDev | pdv_p, |

| int | state | ||

| ) |

Enable/Disable frame count in the first word of each frame.

| pdv_p | The open EDT device handle. |

| state | Enable (1) or disable (0) the first word frame count. |

When enabled the first word of the frame is the frame count: a 16-bit flag of 0x3333 in the MSBs and a 16-bit framecount in the LSBs. It replaces the first 32-bit word of DMA or internally generated data, after any interleaving.

When clear, the first word is the DMA data or generated data per pdv_cls_set_firstfc().

| void pdv_cls_set_datacnt | ( | PdvDev | pdv_p, |

| int | state | ||

| ) |

Enable/Disable internal image data generation; allows image data to come from the counters instead of the DMA stream.

| pdv_p | The open EDT device handle. |

| state | Enable (1) to output internally-generated data, disable (0) to output data from the host via DMA. |

The simulated 32-bit data generated has a 16-bit count in the LSBs; the 16 MSBs are an inverted version of the LSBs. The count is cleared to zero at the start of each frame. Thus the first 32-bit word of each frame is 0xffff0000, the second is fffe0001, and so on. The CLS treats this data as little-endian, so the fourth 8-bit pixel of the frame has a value of 0x01.

When set, also setting SMALLOK (pdv_cls_set_smallok()) stops the simulator at the start of the next frame, to enable getting a single frame of counter data.

| void pdv_cls_set_led | ( | PdvDev | pdv_p, |

| int | state | ||

| ) |

Controls state of the board's green LED.

| pdv_p | The open EDT device handle. |

| state | Enable (1) to turn on LED, disable (0) to turn off LED. |

| void pdv_cls_set_trigsrc | ( | PdvDev | pdv_p, |

| int | select | ||

| ) |

Selects which input pins to look at for external trigger; CC1 or CC2.

| pdv_p | The open EDT device handle. |

| select | Set input trigger to CC2 (1) or CC1 (0). |

| void pdv_cls_set_trigpol | ( | PdvDev | pdv_p, |

| int | polarity | ||

| ) |

Set the trigger polarity.

| pdv_p | The open EDT device handle. |

| polarity | Set trigger polarity to positive (1) or negative (0). |

For more information see: pdv_cls_set_trigsrc(), pdv_cls_set_trigframe(), pdv_cls_set_trigline()

| void pdv_cls_set_trigframe | ( | PdvDev | pdv_p, |

| int | state | ||

| ) |

Enable/Disable frame-valid triggering; if enabled CLS waits at the start of each frame until a trigger is detected.

| pdv_p | The open EDT device handle. |

| state | Enable (1) or disable (0) frame-valid triggering. |

For more information see: pdv_cls_set_trigsrc(), pdv_cls_set_trigpol(), pdv_cls_set_trigline()

| void pdv_cls_set_trigline | ( | PdvDev | pdv_p, |

| int | state | ||

| ) |

Enable/Disable line-valid triggering; if enabled CLS waits at the start of each raster until a trigger is detected.

| pdv_p | The open EDT device handle. |

| state | Enable (1) or disable (0) line-valid triggering. |

A Dalsa linescan camera starts the next raster when it detects a rising edge on the CC1 line.

For more information see: pdv_cls_set_trigsrc(), pdv_cls_set_trigpol(), pdv_cls_set_trigframe()

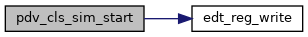

| void pdv_cls_sim_start | ( | PdvDev | pdv_p | ) |

Clear the CFG register including the FIFO_RESET bit (bit 3, 0x08) which clears the FIFO and starts the CLS.

| pdv_p | The open EDT device handle. |

| void pdv_cls_sim_stop | ( | PdvDev | pdv_p | ) |

Set the CFG register FIFO_RESET bit (bit 3, 0x08) which stops the CLS.

| pdv_p | The open EDT device handle. |

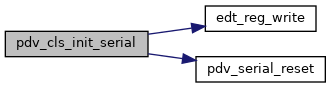

| void pdv_cls_init_serial | ( | PdvDev | pdv_p | ) |

Re-intializes and enables the serial communication.

| pdv_p | The open EDT device handle. |

Rarely used since the serial gets initialized at device open.

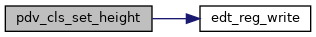

| void pdv_cls_set_height | ( | PdvDev | pdv_p, |

| int | height, | ||

| int | vblank | ||

| ) |

Set the height of outgoing frames, as well as the number of blank lines (vblank) between valid lines.

| pdv_p | The open EDT device handle. |

| height | Frame height; lines of active data. |

| vblank | Vertical blanking, in lines. |

For other outgoing frame settings see: pdv_cls_set_width(), pdv_cls_set_depth(), pdv_cls_set_line_timing()

| void pdv_cls_set_width | ( | PdvDev | pdv_p, |

| int | width, | ||

| int | hblank | ||

| ) |

Set the width of outgoing frames, as well as the number of blank columns (hblank) between valid columns.

| pdv_p | The open EDT device handle. |

| width | Frame width; columns or pixels of active data. |

| hblank | Horizontal blanking, in columns. |

Before calling ensure the registers can be properly set via one of the below methods.

This overwrites the horizontal line valid start values with new values based on the width and blanking, as well as sets ReadValid to the full width.

Follow this with a call to pdv_cls_set_line_timing() if you want to set specific values for those.

For other outgoing frame settings see: pdv_cls_set_height(), pdv_cls_set_depth(), pdv_cls_set_line_timing()

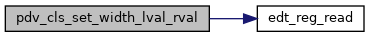

| void pdv_cls_set_width_lval_rval | ( | PdvDev | pdv_p, |

| int | width, | ||

| int | hblank, | ||

| int | hlvstart, | ||

| int | hlvend, | ||

| int | hrvstart, | ||

| int | hrvend | ||

| ) |

Set the width of outgoing frames, as well as the number of blank columns (hblank) between valid columns, start and end of both line valid and read valid.

| pdv_p | The open EDT device handle. |

| width | Frame width; columns or pixels of active data. |

| hblank | Horizontal blanking, in columns. |

| hlvstart | Horizontal LVAL start; column on which the line signal is valid (high). |

| hlvend | Horizontal LVAL end; column on which the line signal is no longer valid (low). |

| hrvstart | Horizontal RVAL start; column on which the read signal is valid (high). |

| hrvend | Horizontal RVAL end; column on which the read signal is no longer valid (low). |

Has the same functionality and warnings as pdv_cls_set_width(), with the inclusion of LVAL and RVAL start and end.

| void pdv_cls_set_depth | ( | PdvDev | pdv_p, |

| int | value | ||

| ) |

Set the depth of outgoing frames.

| pdv_p | The open EDT device handle. |

| value | Frame depth, in bits of data. |

For other outgoing frame settings see: pdv_cls_set_height(), pdv_cls_set_width(), pdv_cls_set_line_timing()

| void pdv_cls_set_clock | ( | PdvDev | pdv_p, |

| double | freq | ||

| ) |

Set the pxiel clock frequency (in MHz).

| pdv_p | The open EDT device handle. |

| freq | The new pixel clock frequency (MHz); valid range is 19.9-85.1, a warning is produced for frequencies outside this range. |

PCI boards, sets the MPC9230 PLL on PCI CD-CLSIM to 3.5 times the requested frequency.

| void pdv_cls_set_fill | ( | PdvDev | pdv_p, |

| u_char | left, | ||

| u_char | right | ||

| ) |

Set the left and right fill values when RVEN (pdv_cls_set_rven()) is enabled.

| pdv_p | The open EDT device handle. |

| left | The 8 bit left fill value (FillA in CLS docs). |

| right | The 8 bit right fill value (FillB in CLS docs). |

Left side uses FillA; right uses FillB.

| void pdv_cls_set_readvalid | ( | PdvDev | pdv_p, |

| u_short | HrvStart, | ||

| u_short | HrvEnd | ||

| ) |

Set the horizontal start and end positions if RVEN (pdv_cls_set_rven()) is enabled.

| pdv_p | The open EDT device handle. |

| HrvStart | Horizontal RVAL start; column on which the line signal is valid (high). |

| HrvEnd | Horizontal RVAL end; column on which the line signal is no longer valid (low). |

| void pdv_cls_set_dvalid | ( | PdvDev | pdv_p, |

| u_char | skip, | ||

| u_char | mode | ||

| ) |

Set the values for Data Valid (DVAL) timing.

| pdv_p | The open EDT device handle. |

| skip | Number of pixel clocks to skip per DVAL strobe. |

| mode | Simulated DVAL signal during blanking. Valid values: 0 low, 1 high, 2 to mirror behavior during active video, 3 always low. |

| void pdv_cls_setup_interleave | ( | PdvDev | pdv_p, |

| short | tap0start, | ||

| short | tap0delta, | ||

| short | tap1start, | ||

| short | tap1delta, | ||

| short | tap2start, | ||

| short | tap2delta, | ||

| short | tap3start, | ||

| short | tap3delta | ||

| ) |

Set the start address and delta for each tap.

| pdv_p | The open EDT device handle. |

| tap0start | The start address for tap 0. |

| tap0delta | The delta for tap 0. |

| tap1start | The start address for tap 1. |

| tap1delta | The delta for tap 1. |

| tap2start | The start address for tap 2. |

| tap2delta | The delta for tap 2. |

| tap3start | The start address for tap 3. |

| tap3delta | The delta for tap 3. |

| int pdv_cls_get_vgap | ( | PdvDev | pdv_p | ) |

Computes the vertical gap (vgap\vblank) value.

| pdv_p | The open EDT device handle. |

| int pdv_cls_get_hgap | ( | PdvDev | pdv_p | ) |

Computes the horizontal gap (hgap/hblank) value.

| pdv_p | The open EDT device handle. |

| double pdv_cls_frame_time | ( | PdvDev | pdv_p | ) |

Computes the frame time in milliseconds.

| pdv_p | The open EDT device handle. |