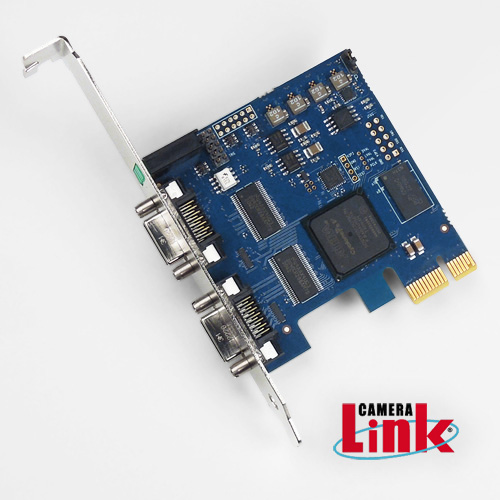

Camera Link simulator over PCI Express Gen3

The VisionLink CLS is a Camera Link simulator that simulates base mode cameras. The board supports the Camera Link 2.0 spec. This includes 1-tap/8-bit, 2-tap/8-bit, 1-tap/10-bit, 2-tap/10-bit, 1-tap/12-bit, 2-tap/12-bit, 1-tap/14-bit, 1-tap/16-bit, 24-bit RGB, at pixel clock frequencies from 20 to 85 MHz. It outputs board-generated or file-based data to facilitate the development and testing of imaging systems, cameras, and software.

Saved data is sent via DMA from host memory at rates of up to 255MB/sec. Board-generated data can be used as an alternative source of output.

VisionLink CLS initialization is performed by text-based configuration scripts. These files are easily modifiable to match the timing parameters of multiple camera models. Triggering of output data is supported over camera control lines (CC1-4).

C language libraries provide access to all simulator functions. These libraries allow the user to define appropriate responses to UART commands from the interface.