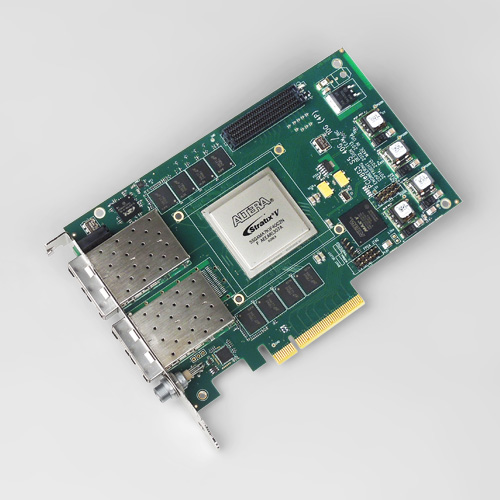

Altera Arria V FPGA | 10Gbps SFP+

The PCIe8 G3 A5-10G is a fast, versatile low-profile PCI Express (PCIe, Gen3) x8 interface, available with either a full or a half-height back panel. It has up to two 10G SFP/+ ports and supports 1/10GbE, OC3/12/48/192 (STM1/4/16/64), or OTU1/2/2e/2f.

Each port on the PCIe8 G3 A5-10G has its own reference clock, programmable for 1–808 MHz, and links to the FPGA for serialization / deserialization (SERDES) and clock recovery.

The FPGA is an Altera Arria V GZ (E3, E5, or E7) with access to a 64-bit wide 2 GB block of DRAM (DDR3), which can act as a data buffer. The FPGA provides up to 8 independent DMA channels via EDT FPGA configuration files. A time code input (1 pps or IRIG‑B) also is included, with an option for either DB9 or BNC cabling.

EDT FPGA configuration files are included to support 1GbE and 10GbE (at the PCS and PMA layers); OC3/12/48/192 and OTU1/2/2e/2f (raw, framed, framed and descrambled); and demultiplexing. Custom files can be requested.